引言

當前,越來越多的通信系統(tǒng)工作在很寬的頻帶上,對于保密和抗干擾有很高要求的某些無線通信更是如此,隨著信號處理器件的處理速度越來越快,數(shù)據采樣的速率也變得越來越高,在某些電子信息領域,要求處理的頻帶要盡可能的寬、動態(tài)范圍要盡可能的大,以便得到更寬的頻率搜索范圍,獲取更多的信息量。因此,通信系統(tǒng)對信號處理前端的A/D采樣電路提出了更高的要求,即希望A/D轉換速度快而采樣精度高,以便滿足系統(tǒng)處理的要求。

可編程門陣列FPGA的出現(xiàn)已經顯著改變了數(shù)字系統(tǒng)的設計方式。應用可編程門陣列FPGA,可使數(shù)字系統(tǒng)設計具有高度的靈活性,因此FPGA的應用越來越廣泛,而新一代FPGA--Virtex Ⅱ-PRO的出現(xiàn)使FPGA的功能更加強大,但隨之而來的是要求提高數(shù)據的傳輸速率,過去人們總是關心如何提高處理器運行速度,而現(xiàn)在關心的是怎樣才能更快地將數(shù)據從一個芯片傳輸?shù)搅硪粋€芯

片。可見,高速數(shù)據采集系統(tǒng)的輸入輸出接口設計就顯得尤為重要。

1 高速采集系統(tǒng)介紹

數(shù)據采集系統(tǒng)原理框圖如圖1所示,輸入的中頻信號經A/D采樣電路采樣后,轉換成LVDS信號送入FPGA中,或通過FPGA的端口RocketIO從高速接口輸出,或通過FPGA的端口LVDS循環(huán)存儲于高速緩存中,再由低速接口輸出。其中,F(xiàn)PGA主要完成對外接口管理、高速緩存的控制和管理。時鐘控制電路對A/D數(shù)據轉換器和可編程門陣列FPGA起同步和均衡作用。

2 輸入輸出接口研究

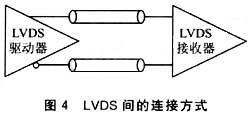

Virtex Ⅱ-PRO系列是在Virtex Ⅱ系列FPGA的基礎上,嵌入了高速I/O接口和IBM PowerPC處理器,它能實現(xiàn)超高帶寬的系統(tǒng)芯片設計,支持LVDS,LVPECL等多種差分接口,適應性很強。其中高速串行(MGT)技術采用了RocketIO技術,在可編程邏輯器件中內嵌了速率為3.125Gb/s的多端串行通信接口,該技術包括千Mb以太網、10千以太網、3GIO、SerialATA、Infiniband和Fibre Channel,為高性能接口提供了完成的解決方案。LVDS(Low Voltage Differential Signaling)信號標準是一種小振幅差分信號技術,如圖2所示,它使用非常低的幅度信號(100-450mV),通過一對平行的PCB走線或平衡電纜傳輸數(shù)據。在兩條平行的差分信號線上流經的電流方向相反,噪聲信號同時耦合到兩條線上,而接收端只關心兩信號的差值,于是噪聲被抵消。由于兩條信號線周圍的電磁場也互相抵消,故差分信號傳輸比單線信號傳輸電磁輻射小很多,從而提高了傳輸效率并降低了功耗。

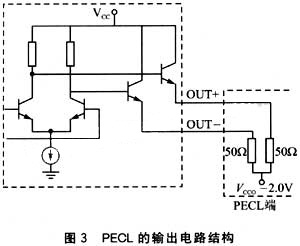

在高速數(shù)據采集系統(tǒng)中,使用了最新的A/D芯片MAX104A。該芯片是Maxim公司的最新產品,采樣頻率可以達到1GHz,采樣精度為8位。芯片輸出是PECL(Positive Emitter-Coupled Logic)電平輸出。PECL信號的擺幅相對ECL要小,適合于高速數(shù)據的串行或并行連接。PECL的輸出電路結構如圖3所示。該電路包含一個差分對管和一對射隨器。輸出射隨器工作在正電壓范圍內,無信號時電流始終存在,這樣有利于提高開關速度,標準的輸出負載接50Ω電阻至VCCO-2V的電平上,如圖3所示,在這種負載條件下,OUT+與OUT-的靜態(tài)電平典型值為UCCO-1.3V,OUT+與OUT-輸出電流為14mA。PECL結構的輸出阻抗很低,典型值為4-5Ω,這表明它有很強的驅動能力。但當負載與PECL的輸出端之間有一段傳輸線時,低阻抗造成的失配將導致信號時域波形的振鈴現(xiàn)象。

3 RocketIO設計

Xilinx公司的Virtex Ⅱ-PRO FPGA采用具有時鐘恢復功能的全雙工串行I/O收發(fā)器,可高效地實施每通道帶寬達到3.125Gb/s的不同協(xié)議設計。收發(fā)器支持高達到每通道3.125Gb/s的數(shù)據速率,并可利用通道捆綁功能滿足各種應用不斷增長的數(shù)據傳輸速率的要求,Virtex Ⅱ-PRO的收發(fā)模塊由物理編碼子層(PCS)和物理介質接入(PMA)構成,其中物理編碼子層提供與FPGA邏輯內的數(shù)字接口,內部包括:循環(huán)冗余碼校驗CRC、8B/10B編解碼器、先進先出緩沖器FIFO;物理介質接入提供與外部媒體的模擬接口,其中包括:20倍時鐘倍頻器、發(fā)送端時鐘生成器、發(fā)送緩沖器、串化器、接收端的時鐘恢復電路,接收緩沖器、解串器、可變速率的全雙工收發(fā)器、可編程的五級差分輸出幅度(擺率)控制和可編程的四級輸出預加重模塊。RocketIO的原始設計是比較復雜的,但幸運的是,Xilinx公司提供了大量成熟的和高效的IP(Intellectual Property)核來使用。如果能夠很好地掌握該工具的使用,將會極大地縮短設計的進度,減少開發(fā)和調試時間,由于IP核是根據Xilinx FPGA器件的特點和結構設計的,直接用Xilinx FPGA底層硬件原語進行描述,可充分地將FPGA的性能開發(fā)出來,其實現(xiàn)結果在面積和速度上都能達到令人滿意的效果。在設計中,還要考慮到以下方面。

(1)參考時鐘

高性能的通信質量要求有高穩(wěn)定性和高精度的時鐘源。抖動和頻偏是衡量時鐘源的兩個重要指標。頻偏是指時鐘標稱頻率與實際頻率的偏差,主要是受晶體精度的影響,由于RocketIO模塊內部將輸入參考時鐘20倍頻,而RocketIO模塊可容忍的輸入參考時鐘抖動公差為40ps,可見參考時鐘的抖動對其性能有直接影響,所以必須選擇性能優(yōu)良的參考時鐘。抖動一般是指一個實際情況下的周期信號每個周期的圖樣相對于該信號理想情況下一個周期圖樣的偏差。抖動產生的原因包括:時鐘晶體本身的機械振動、器件的熱噪聲和電源串入噪聲等。抖動可以分為確定性抖動和隨機抖動,確定性抖動包括信號在傳輸中煤質損耗、碼間串擾(ISI)等周期性因素導致的抖動;隨機抖動是由半導體器件熱噪聲、電源波動等共模隨機噪聲源導致的。在Virtex Ⅱ-PRO系列FPGA中,RocketIO模塊集中分布在上、下4個通道中,當RocketIO工作在2.0 Gbaud以上時,參考時鐘應采用差分輸入方式(如LVDS、LVPECH),由上述4個通道的專用差分時鐘引腳輸入,至相同時鐘信號引入不必要的抖動,在2.0 Gbaud速率以下應用時,不要用FPGA內部的DCM來生成RocketIO的輸入時鐘,因為經DCM倍頻的時鐘會引入較大的抖動,使RocketIO的接收鎖相環(huán)無法穩(wěn)定地鎖定發(fā)送時鐘,致使系統(tǒng)無法正常工作。

(2)復位

在Virtex Ⅱ-PRO系列FPGA中,RocketIO模塊的復位引腳分為發(fā)送(TX_RESET)和接收(RX_RESET)兩部分。由于DCM在輸出時鐘鎖定在設定值前,輸出時鐘處于不穩(wěn)定狀態(tài),不能用作內部邏輯電路時鐘,所以要在DCM時鐘輸出鎖定有效,并經過適當延遲后才可將片內邏輯復位。RocketIO模塊要求復位輸入至少保持2個USRCLK時鐘周期來完成內部FIFO的初始化。

(3)PCB設計

在PCB的設計中,應使差分線對內的長度相互匹配,以減少信號扭曲。為使設計傳輸速率達到2.0 Gbaud,在差分線對內部每個走線區(qū)間內的實際布線公差應控制在5 mil內。差分線對內兩條線之間的距離應盡可能小,以使外部干擾為共模特征。差分線對間的距離應盡可能保持一致,以降低差分阻抗分布的不連續(xù)性。采用電源層作為差分線的信號回路,因為電源平面有最小的傳輸阻抗,從而減少噪聲,由于每個過孔可帶來0.5-1.0dB的損耗,應盡量減少過孔數(shù)目。過孔的通孔和焊盤應有盡量小的物理尺寸,并且在通孔穿越的未連接不加焊盤,差分對內的過孔不僅在數(shù)量上要匹配,而且在放置的位置上也要接近,以使阻抗分布盡量一致,避免導致阻抗不連續(xù)的90°走線,而要用圓弧或45°折線來代替。走線時應使向左、向右折角的數(shù)量接近,這樣可減少信號經差分線傳輸引起的扭曲。在模擬數(shù)字混合系統(tǒng)設計中,首先,應在電源和地線之間加上去耦電容;其次,盡量加寬電源和地線寬度,最好是地線比電源線寬,使得地線寬度>電源線寬度>信號線寬度;第三,使用統(tǒng)一地,而將PCB分區(qū)為模擬部分和數(shù)字部分,模擬信號在電路板所有層的模擬區(qū)內布線,而數(shù)字信號在數(shù)字電路區(qū)內布線,在這種情況下,數(shù)字信號返回電流不會流入到模擬信號的地。經過以上設計,噪聲影響明顯降低。

4 接口解決方案

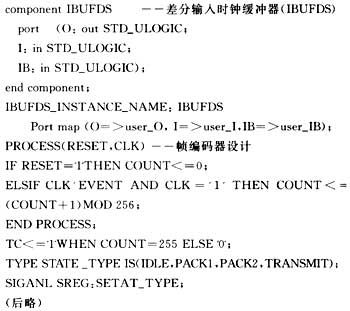

隨著高速數(shù)據傳輸業(yè)務需求的增加,如何高質量地解決高速IC芯片的相互連接變得越來越重要,低功耗及高的信噪比是有待解決的主要問題。本文所介紹的高速采集系統(tǒng)中芯片間有兩種接口:PECL和LVDS,如何進行兩接口相互連接就成為一個影響系統(tǒng)性能的關鍵因素,LVDS的輸入與輸出都是內匹配的,所以LVDS間的連接可采用圖4所示的直接連接,在FPGA內,需對差分輸入時鐘緩沖器(IBUFDS),差分輸入的全局時鐘緩沖區(qū)(IBUFGDS)和差分輸出時鐘緩沖器(OBUFDS)例化,在本項目的應用中,發(fā)送及接收FIFO的設計用了雙口塊內存(Block RAM),時鐘倍頻器用了延遲鎖定環(huán)(DLL),幀解碼器由30位并行數(shù)據產生器、同步字檢測陣列和接收狀態(tài)機組成。

FPGA的部分代碼如下:

PECL間的連接一般常用直流耦合。在直流耦合情況下,PECL輸出設計驅動50Ω負載至(VCC-2V),電路如圖5所示。

FPGA的部分代碼如下:

經實際測試,輸入輸出指標均符號系統(tǒng)要求,在硬件電路設計中,由于LVDS信號的偏置電壓為1.25V,電壓擺幅只有350mV,傳輸速率≥100Mb/s;因此,電路板制作至關重要,要求至少使用四層板。為使干擾信號以共模方式加到差分線對上(不影響數(shù)據正確性),要求差分線對間的距離盡可能小。電源方面,F(xiàn)PGA芯片上電時要求有大于500mA的驅動電流,同時,由于多個輸出引腳的電位速度變化,要求每對電源和地引腳都要良好旁路。

5 結論

本文給出了基于FPGA高速數(shù)據采集系統(tǒng)中的輸入輸出接口的實現(xiàn),介紹了高速傳輸系統(tǒng)中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數(shù)傳系統(tǒng)中得到應用。RocketIO傳輸速度可以達到2.5Gbaud,LVDS總線上的傳輸速率可以達到120Mb/s,系統(tǒng)性能穩(wěn)定。