1 引言

直接數字頻率合成器(DDS)技術,具有頻率切換速度快,很容易提高頻率分辨率、對硬件要求低、可編程全數字化便于單片集成、有利于降低成本、提高可靠性并便于生產等優點。目前各大芯片制造廠商都相繼推出采用先進CMOS工藝生產的高性能和多功能的DDS芯片,專用DDS芯片采用了特定工藝,內部數字信號抖動很小,輸出信號的質量高。然而在某些場合,由于專用的DDS芯片的控制方式是固定的,故在工作方式、頻率控制等方面與系統的要求差距很大,這時如果用高性能的FPGA器件設計符合自己需要的DDS電路就是一個很好的解決方法,它的可重配置性結構能方便的實現各種復雜的調制功能,具有很好的實用性和靈活性。

2 DDS調頻信號發生器框圖設計

3 DDS調頻信號發生器FPGA電路設計

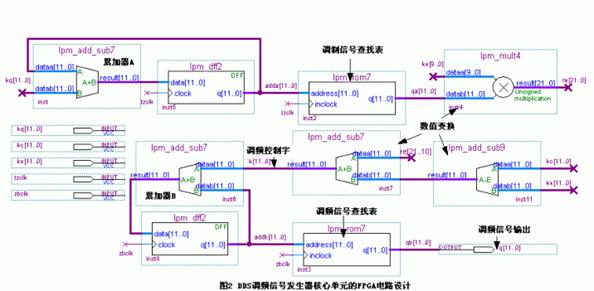

圖2給出了DDS調制信號發生器核心單元的FPGA電路設計圖。其設計方案采用ALTERA公司的Cyclone系列EP1C6T144C6芯片,加法器為12位,調制信號波形存儲器為4096×12BIT,載波信號波形存儲器為4096×12BIT,系統時鐘為80MHz;設計性能參數:載波頻率可達10MHz(為確保波形不失真,一周期至少取8點),調制頻率范圍0~100K,調頻深度0~10。外部電路輸入有調制信號頻率控制字Kh[11..0],載波信號頻率控制字Kc[11..0],頻偏控制字Kx[11..0],調制信號系統時鐘TZCLK,載波信號系統時鐘ZBCLK。Kh[11..0]經累加器A輸出累加相位ADDA[11..0]作為調制信號查找表的地址,波形數據Qa[11..0]和Kx[11..0]和Kc[11..0]經過數值變換后輸出調頻控制字K[11..0]。K[11..0]經累加器B輸出累加相位ADDB[11..0]作為調頻信號查找表的地址,波形數據Qb[11..0]經外部DAC轉換和低通濾波得到調頻信號波形。其中,在兩個累加器后相連的DFF緩沖器有助于消除毛刺的影響,進一步確保系統的穩定性和可靠性。

4 仿真及實驗

取載波系統時標頻率1MHz,調制信號系統時標頻率100KHz,相位累加器位數8位,兩個波形存儲器地址位數和數據位數都為8位。用QUERTUS Ⅱ 3.0 仿真,見圖3;

圖3 DDS調頻波仿真圖(QUERTUS II)

用matlab 6.5仿真見圖4;

用AEDK-EDA實驗箱下載(其FPAG芯片為EPF10K10TC144-4),D/A轉換及單極性輸出電路用ispPAC20芯片實現,通過Tektronix TDS3054B示波器觀察波形,結果見圖5。其中D/A位數為8,測量范圍-4-+4V,載波信號峰值1.414V,由圖4和圖5頻率調制解調波形數據可得載波頻率為14.2kHz,誤差-3.06%;調制頻偏為480Hz,誤差-1.69%;調制度為M=10.21%,誤差2.1%,調制頻率為4.82kHz,誤差-1.23%。從實驗結果可以看出本文提供的設計理論及設計電路的不但正確、可行,并具有良好的性能參數。所有設計、仿真及實驗結果的一致,為DDS調頻信號發生器FPGA實現提供了優良的設計方案。

圖4 DDS調頻波仿真圖(matlab)

圖5 DDS調頻波實驗結果圖

5 總結

用FPGA實現DDS調頻信號電路較采用專用DDS芯片更為靈活,只要改變FPGA中ROM內的數據和控制參數,DDS就可以產生任意調制波形,且分辨率高,具有相當大的靈活性。相比之下,DDS的功能完全取決于設計需求,可以復雜也可以簡單,而且FPGA芯片還支持在系統現場升級。另外,將DDS設計嵌入到FPGA芯片所構成的系統中,其系統成本并不會增加多少,而購買專用芯片的價格則是前者的很多倍。所以采用FPGA來設計DDS系統具有很高的性價比。