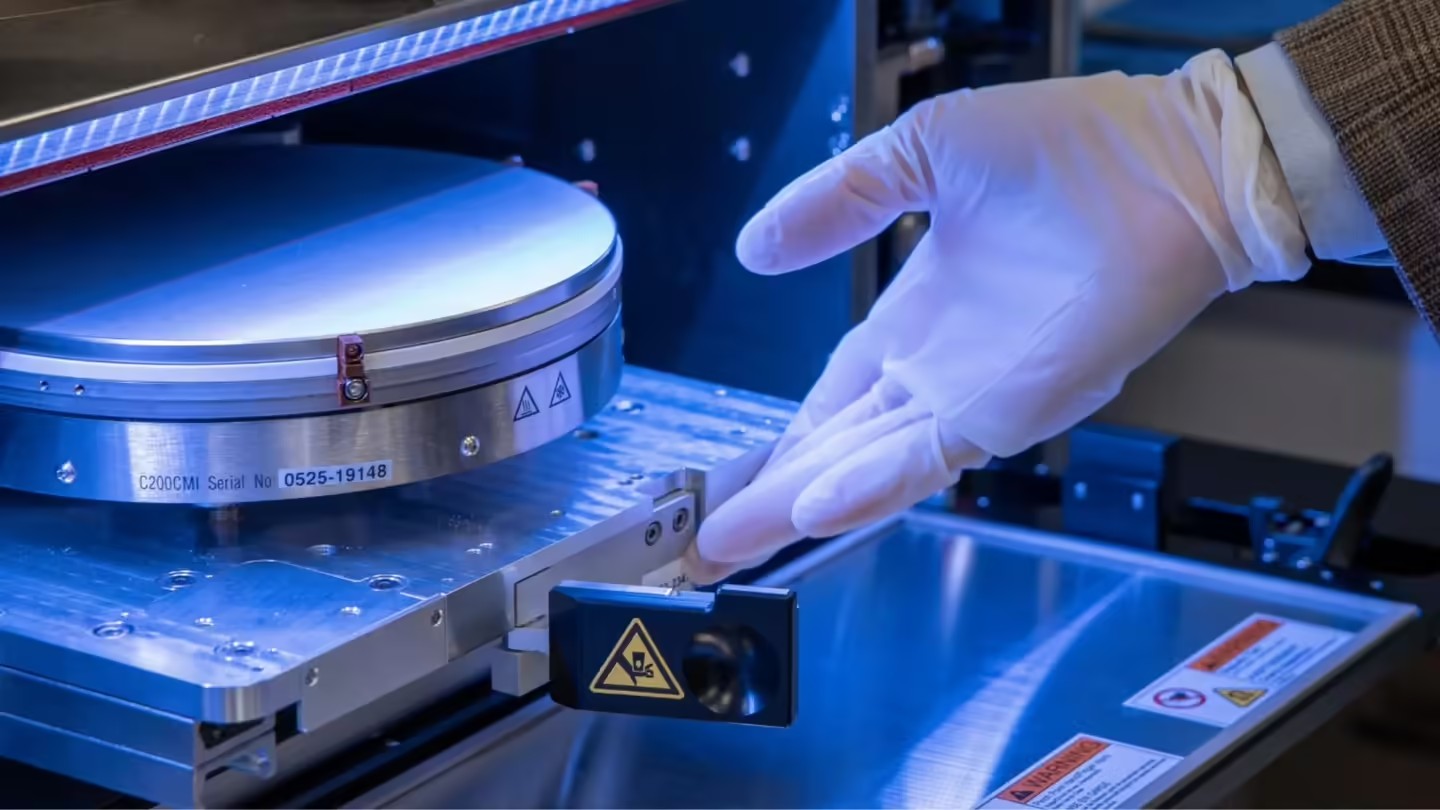

12 月 14 日消息,據(jù) InterestingEngineering 報(bào)道,美國(guó)工程師研發(fā)出一種具有獨(dú)特架構(gòu)的新型多層計(jì)算機(jī)芯片,有望開啟人工智能硬件新紀(jì)元。

研究團(tuán)隊(duì)指出,在硬件測(cè)試和仿真中,這款新型三維(3D)芯片的性能比傳統(tǒng)二維(2D)芯片高出近一個(gè)數(shù)量級(jí)。

據(jù)了解,與當(dāng)前主流的平面化 2D 芯片不同,該新型原型芯片的關(guān)鍵超薄組件如同摩天大樓的樓層般垂直堆疊,其內(nèi)部的垂直布線則如同大量高速電梯,可實(shí)現(xiàn)快速、大規(guī)模的數(shù)據(jù)傳輸。該芯片憑借創(chuàng)紀(jì)錄的垂直互連密度以及精心交織的存儲(chǔ)單元與計(jì)算單元,有效規(guī)避了長(zhǎng)期制約平面芯片性能提升的瓶頸問題。

斯坦福大學(xué)電氣工程系 William E. Ayer 講席教授、計(jì)算機(jī)科學(xué)教授、同時(shí)也是描述該芯片成果論文的主要負(fù)責(zé)人 Subhasish Mitra 表示:“這為芯片制造與創(chuàng)新開啟了一個(gè)新時(shí)代。正是此類突破,才能滿足未來人工智能系統(tǒng)對(duì)硬件性能千倍提升的需求。”

盡管學(xué)術(shù)界此前已研制過實(shí)驗(yàn)性 3D 芯片,但此次是首次在商業(yè)晶圓代工廠成功制造出具備明確性能優(yōu)勢(shì)的 3D 芯片。

研究團(tuán)隊(duì)還指出,在傳統(tǒng) 2D 芯片上,所有組件都布置于單一平面,內(nèi)存分布稀疏且有限,數(shù)據(jù)只能通過少數(shù)幾條冗長(zhǎng)而擁擠的路徑傳輸。由于計(jì)算單元的運(yùn)行速度遠(yuǎn)快于數(shù)據(jù)移動(dòng)速度,同時(shí)芯片無法在附近集成足夠內(nèi)存,系統(tǒng)常常被迫等待數(shù)據(jù),這一現(xiàn)象被工程師稱為“內(nèi)存墻”(memory wall),即處理速度超過芯片數(shù)據(jù)傳輸能力的臨界點(diǎn)。

卡內(nèi)基梅隆大學(xué)電氣與計(jì)算機(jī)工程助理教授、該論文資深作者 Tathagata Srimani 表示:“通過將內(nèi)存與計(jì)算單元垂直集成,我們可以更快地傳輸更多數(shù)據(jù),就像高層建筑中的多部電梯能同時(shí)運(yùn)送大量住戶上下樓層一樣。”Srimani 最初是在 Mitra 指導(dǎo)下從事博士后研究時(shí)啟動(dòng)了這項(xiàng)工作。

斯坦福大學(xué)、卡內(nèi)基梅隆大學(xué)、賓夕法尼亞大學(xué)和麻省理工學(xué)院的工程師們與 SkyWater Technology 公司合作開發(fā)了這款 3D 芯片。

初步硬件測(cè)試顯示,該原型芯片的性能已比同類 2D 芯片高出約 4 倍。對(duì)更高堆疊層數(shù)的未來版本進(jìn)行的仿真表明,性能提升更為顯著:在真實(shí) AI 工作負(fù)載(包括源自 Meta 開源 LLaMA 模型的任務(wù))下,增加更多層級(jí)的設(shè)計(jì)可實(shí)現(xiàn)最高達(dá) 12 倍的性能提升。

研究團(tuán)隊(duì)還聲稱,該設(shè)計(jì)為實(shí)現(xiàn)能效-延遲乘積(Energy-Delay Product, EDP)提升 100 至 1000 倍開辟了一條切實(shí)可行的路徑。EDP 是衡量速度與能效平衡的關(guān)鍵指標(biāo)。通過大幅縮短數(shù)據(jù)傳輸距離并增加大量垂直通路,該芯片能夠同時(shí)實(shí)現(xiàn)更高的吞吐量和更低的單位操作能耗,這種組合長(zhǎng)期以來被認(rèn)為是傳統(tǒng)平面架構(gòu)難以企及的目標(biāo)。

賓夕法尼亞大學(xué)電氣與系統(tǒng)工程助理教授、該研究共同作者 Robert M. Radway 表示:“‘內(nèi)存墻’與‘微縮墻’(miniaturization wall)構(gòu)成了致命組合。我們通過緊密集成內(nèi)存與邏輯單元,并以極高密度向上構(gòu)建,正面迎擊這一挑戰(zhàn)。這就好比計(jì)算領(lǐng)域的曼哈頓 —— 我們能在更小的空間內(nèi)容納更多‘居民’。”