1 DDS" title="DDS">DDS結(jié)構(gòu)原理

DDS是一種從相位概念出發(fā)直接合成所需波形的數(shù)字頻率合成技術(shù),主要通過查找波形表實現(xiàn)。由奈奎斯特抽樣定理可知,當(dāng)抽樣頻率大于被抽樣頻率的2倍時,通過抽樣得到的數(shù)字信號可通過一個低通濾波器還原成原來的信號。

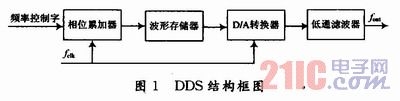

DDS的工作原理為:在參考時鐘的驅(qū)動下,相位累加器對頻率控制字進行線性累加,得到的相位碼對波形存儲器尋址,使之輸出相應(yīng)的幅度碼,經(jīng)過模/數(shù)轉(zhuǎn)換器得到相應(yīng)的階梯波,最后再使用低通濾波器對其進行平滑,得到所需頻率的平滑連續(xù)的波形,其結(jié)構(gòu)如圖1所示。

相位累加器由N位加法器和N位累加寄存器級聯(lián)構(gòu)成。每經(jīng)過一個時鐘脈沖fclk,加法器就將頻率控制字與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送至累加寄存器的數(shù)據(jù)輸入端。相位累加器輸出的數(shù)據(jù)就是合成信號的相位,相位累加器的溢出頻率就是DDS的輸出信號頻率。用相位累加器輸出數(shù)據(jù)作為波形存儲器(ROM)的相位取樣地址,這樣就可以把存儲在波形存儲器內(nèi)的波形抽樣值(二進制編碼)經(jīng)查找表查出,完成相位到幅度的轉(zhuǎn)換。

DDS模塊的輸出頻率是系統(tǒng)工作頻率、相位累加器比特數(shù)N以及頻率控制字三者的一個函數(shù),其數(shù)學(xué)關(guān)系由式(1)給出。

它的頻率分辨率,即頻率的變化間隔為K/2N。

2 系統(tǒng)功能單元實現(xiàn)

該系統(tǒng)設(shè)計是針對DDS的基本結(jié)構(gòu),以FPGA" title="FPGA">FPGA為核心,加上外圍電路而實現(xiàn)的。

2.1 相位累加器

相位累加器由8位加法器與8位寄存器級聯(lián)構(gòu)成。累加器將加法器在上一個時鐘作用后所產(chǎn)生的相位數(shù)據(jù)反饋到加法器的輸入端:使加法器在下一個時鐘作用下繼續(xù)與頻率控制字data相加,實現(xiàn)相位累加,當(dāng)相位累加器累加結(jié)果等于或大于256(當(dāng)N=8時),則產(chǎn)生1次溢出,完成1個周期波形輸出。該相位累加器采用Verilog語言設(shè)計實現(xiàn)。

2.2 波形存儲器

以相位累加器輸出數(shù)據(jù)作為波形存儲器的取樣地址,進行波形的相位—幅碼轉(zhuǎn)換,即可在給定的時間上確定輸出的波形的抽樣幅碼。N位的尋址ROM相當(dāng)于把0~2π的正弦信號離散成具有2N個樣值的序列。若波形存儲器有D位數(shù)據(jù)位,則各樣值的幅碼以D位二進制數(shù)值保存在該模擬ROM中,按照不同地址輸出相應(yīng)相位的正弦信號的幅碼數(shù)值。為了更加有效的表示波形,當(dāng)然期望波形存儲器輸出的二進制值位數(shù)越多越好。但是查找表的設(shè)計和D/A轉(zhuǎn)換器的選擇是相關(guān)的,因此需要選擇位數(shù)高的D/A轉(zhuǎn)換器。本文設(shè)計的正弦表,具有16b輸出,采樣點為256。

2.3 D/A轉(zhuǎn)換電路的實現(xiàn)

D/A轉(zhuǎn)換單元是繼波形數(shù)據(jù)產(chǎn)生單元之后,將數(shù)字量形式的波形幅值轉(zhuǎn)換成所要求的合成頻率的模擬量形式信號。DAC輸出信號實際上是階梯模擬信號,需在D/A轉(zhuǎn)換后利用低通濾波器對波形進行平滑處理。在此,用Maxim公司生產(chǎn)的A/D換器MAX5885芯片。該芯片需要將輸入時鐘信號轉(zhuǎn)換為差分輸入,且由外部芯片MAX6161提供1.2 V的參考電壓,D/A轉(zhuǎn)換后的差分輸出經(jīng)變壓器轉(zhuǎn)換后即可得到所需的信號:

![]()

3 系統(tǒng)軟件設(shè)計

3.1 累加控制模塊的設(shè)計

相位累加器主要完成相位累加,實現(xiàn)輸出波形頻率可調(diào)的功能。該模塊采用Verilog HDL語言來實現(xiàn),若要求DDS系統(tǒng)精度高,相位累加器的位數(shù)N需較大。這里取N=8,它的Verilog HDL關(guān)鍵代碼如下:

其中,data信號為8位的頻率控制字,通過改變data的值可以實現(xiàn)不同頻率波形的輸出。

3.2 波形存儲器的設(shè)計

針對不同的可編程器件,ROM查找表的設(shè)計采用的方法也不相同。主要是基于IP核Single Port BlockMemory和Verilog選擇語句這兩種方法。使用SinglePort Block Memory的波形存儲表只需要產(chǎn)生數(shù)據(jù)文件*.mif或*.coe,然后直接在定制Single Port BlockMemory時,添加數(shù)據(jù)文件即可。不過這種方法在FPGA支持內(nèi)部嵌入式陣列塊(EAB)時才可以使用;使用Verilog選擇語句比較直觀,但當(dāng)輸入數(shù)據(jù)量大的

這種方法是比較繁瑣的。此次設(shè)計采用第一種方法。

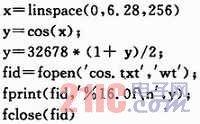

coe文件是在編譯和仿真過程中作為存儲器(ROM或RAM)初始化輸入的文件,即memory initializationfile。創(chuàng)建coe文件的方式有很多種,在這次設(shè)計中,在Matlab中采用C語言來生成coe文件。coe文件編寫格式如下:

將生成的cos.txt文件的后綴該為.coe,打開文件并將最后一行的逗號改為分號,并在文件的最開始添加下面兩行:

最后保存文件退出,并加載到Single Port BlockMemory所生成的ROM中。加載時要特別注意數(shù)據(jù)基數(shù)和數(shù)據(jù)長度的參數(shù)設(shè)置。

4 系統(tǒng)的功能仿真和驗證分析

累加控制器、ROM查找表組成一個整體,實現(xiàn)了一個基本的DDS系統(tǒng)。該設(shè)計以原子鐘(33 MHz)為基準(zhǔn)頻率輸入,取累加器為32位,實現(xiàn)輸出頻率為700 kHz的信號。

5 結(jié)語

直接數(shù)字頻率合成(DDS)技術(shù)屬第三代頻率合成技術(shù),與第二代基于鎖相環(huán)頻率合成技術(shù)相比,利用DDS技術(shù)合成的輸出波形具有良好的性能指標(biāo)本。設(shè)計采用Xilinx公司Spartan-3系列的XC3S200芯片和高速16位D/A轉(zhuǎn)換器MAX5885。在DDS的工作原理的基礎(chǔ)上,介紹基于FPGA實現(xiàn)DDS的設(shè)計方法。 通過設(shè)置參數(shù)可以靈活控制輸出頻率和分辨率。設(shè)計出具有精度高,選擇參數(shù)控制輸出信號,產(chǎn)生一個理想的波形。從測試結(jié)果可看出,該系統(tǒng)工作穩(wěn)定、可靠,并具有較好的參考與實用價值。