摘要:隨著數字化生活的到來,數據采集系統在日常生活中的應用越來越顯著。模擬信號和數字信號之間的轉換已成為計算機控制系統中不可缺少的環節。較傳統數據采集系統,以可編程邏輯器件實現的數據采集系統具有時鐘頻率高,內部延時小,速度快,效率高,組成形式靈活等特點。

關鍵詞:CPLD;數據采集;VHDL;狀態機

數據采集系統具有極強的通用性,可廣泛應用于軍事、工業生產、科學研究和日常生活中。隨著計算機的普及,數據采集系統在日常生活中的應用越來越顯著。由于基于DSP芯片的高速電子器件成本和制作工藝,以及高密集的技術含量,使得高速數據采集卡的價格昂貴。而復雜可編程邏輯器件(CPLD)能夠將大量的邏輯功能集成于一個單片集成電路中,以其時鐘頻率高,內部延時小,速度快,效率高,組成形式靈活等特點在高速數據采集方面有著單片機和DSP無法比擬的優勢。

1 設計思路

該系統由數據輸入單元、數據處理單元、數據輸出單元三大部分組成。其中數據輸入單元是由狀態機控制ADC0809實現。輸入信號可以是各種形式,它可以是語音信號、調制后的電話信號、編碼的數字信號、壓縮的圖像信號,也可以是各種傳感器輸出的信號。A/D能將模擬信號變換成數字信號,但必須滿足香農采樣定理,也就是為了保證不丟失信息的所有信息,采樣頻率必須高于輸入信號最高頻率的2倍。A/D變換后得到的數字信號輸人到CPLD芯片;再由CPLD芯片對該數字信號進行各種數字信號算法的處理。經過處理后的數字信號再經過數/模轉換器ADC0832將其輸出。

2 系統各部分的功能及實現

2.1 數據輸入電路

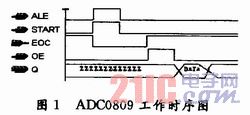

數據輸入電路主要是由狀態機控制ADC0809實現。其中START為轉換控制信號,高電平有效;ALE是3位通道選擇地址(ADDC,ADDB,ADDA)信號的鎖存信號,高電平有效;EOC是轉換情況狀態信號(類似于AD574的STATUS),當啟動轉換約100 μs后,EOC產生一個高電平,以示轉換結束,轉換期間一直處于低電平。一旦START有效后,狀態信號EOC即變為低電平,表示進入轉化狀態。轉換結束后,EOC將變為高電平。OE為數據輸出允許信號,當OE為高電平時,則控制打開三態緩沖器,把轉換好的8位數據結果輸至數據總線。其工作時序如圖1所示。

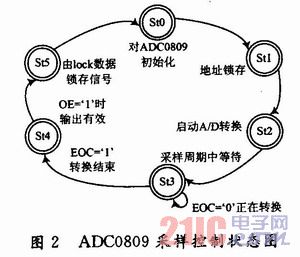

對ADC0809的工作過程分析可知:其工作處于6個狀態。在狀態St1中,ALE高電平將ADC0809的8路采樣輸入通道地址存入ADC0809地址鎖存器中。在狀態St3中需要對ADC0809工作狀態信號EOC進行循環檢測,如果為低電平,表示轉換沒有結束,仍需要停留在St3狀態中等待,直到EOC變成高電平后才說明轉換結束,在下一時鐘脈沖到來時轉向狀態St4。在狀態St4,由狀態機向ADC0809發出轉換好的8位數據輸出命令,這一狀態周期同時可作為數據輸出穩定周期,以便能在下一狀態中向鎖存器中鎖入可靠的數據。在狀態St5,由狀態機向CPLD中的鎖存信號(LO-CK的上升沿),將ADC-0809輸出的數據進行鎖存。其采樣控制狀態圖如圖2所示。

2.2 數據處理電路

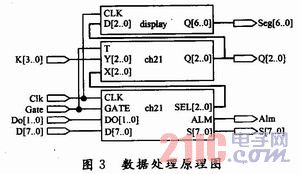

數據處理電路通過VHDL程序實現,該電路的主要功能是對外部輸入信號進行循環檢測,當k1為1時,該器件處于數據采集和處理模式。這里的數據處理就是對其輸入的數字信號進行擴大2倍或縮小到原來的1/2,其中fun用來選擇輸入方式。在采集數據的時候還可以選擇所采數據是ADC0809中的哪一路,并完成在七段數碼器上顯示。其原理如圖3所示。

2.3 數據輸出電路

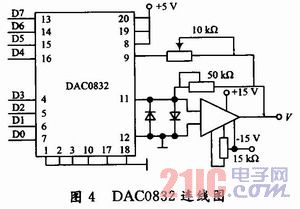

數據輸出電路由數/模轉換器DAC0832實現,ADC0832為8位分辨率A/D轉換芯片,其內部電源輸入與參考電壓的復用,使得芯片的模擬電壓輸入在0~5 V之間。D/A轉換結果采用電流形式輸出。應得到相應的模擬電壓信號,所以通過一個高輸入阻抗的線性運算放大器實現。其連線如圖4所示。

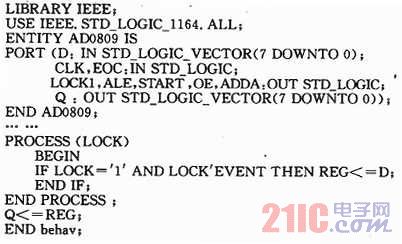

3 電路的VHDL描述

數據采集控制電路、數據處理電路均是使用硬件描述語言VHDL(Very High Speed Integrated Circuit Hatdware Description Langu-age)設計而成。例如:數據采集控制模塊設計如下:

VHDL語言具有多層次的電路設計描述功能,既可描述系統級電路,也可以描述門級電路;描述方式既可以采用行為描述、寄存器傳輸描述或者結構描述,也可以采用三者的混合描述方式。VHDL語言的強大描述能力還體現在它具有豐富的數據類型,采用VHDL語言描述硬件電路時,設計人員并不需要首先考慮選擇進行設計的器件。這樣做的好處是可以使設計人員集中精力進行電路設計的優化,而不需要考慮其他的問題。當硬件電路的設計描述完成以后,VHDL語言允許采用多種不同的器件結構來實現。

4 系統的波形仿真

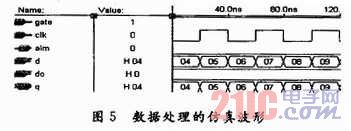

在數據處理電路中,當gate=‘1’,整個器件處于數據采集及處理模式,選擇不同的工作方式,即fun值,可實現不同的數據處理,當do為O時,其波形仿真如圖5所示。從仿真波形中可以看出輸入數據等于輸出數據,在通過輸出運放,使輸出值增大2倍,從而使輸出數據為輸入數據的2倍。

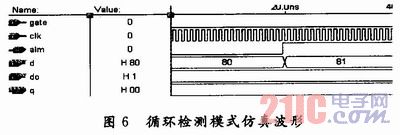

在數據處理電路中,當gate=‘0’,整個器件處于循環檢測的模式,當輸入數據超出預設值時就進行報警,即alm=‘1’,當無輸入值大于預設值時,就進行循環檢測。其波形仿真如圖6所示。

5 結語

設計了基于CPLD的多路異步數據采集系統,系統中使用狀態機控制數據的采集,使用ADC0832進行數/模轉換。同時利用CPLD強大的數字處理功能和高密集成的特點,降低了硬件的成本,簡化了電路設計,并配合軟件增加了系統的靈活性和可擴充性,具有很好的經濟效益和社會效益。