LED全彩同步控制系統具有高性能實時顯示、節能、環保等優點,成為現代信息發布的重要媒體。本設計改變傳統設計中采集顯卡VESA信號接口、使用并行多根總線傳送數據的方式,改用采集DVI接口、通過網口傳輸數據,既節省成本也提高了傳輸效率和傳輸質量。另外,該設計還采用一系列新技術,例如使用高集成度FPGA作為主控制模塊、使用大容量SDRAM代替高成本的等容量SRAM、采用信號包復用技術同步傳送顯示數據和控制數據、采用高效率的灰度切片算法等等。LED同步屏控制系統具有成本低、顯示面積大、顯示穩定、刷新率高等特點,是目前市面上非常具有競爭力的顯示控制方案。

1 系統原理和結構

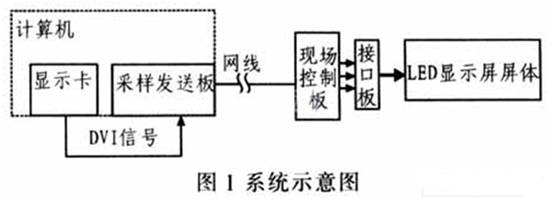

系統整體架構如圖1所示,主要由兩部分組成:采樣發送板(STR)和現場控制板(FRC)。通過大規模邏輯及其他組件,實時同步采集計算機輸出的顯示數據,通過高速緩存、格式轉換后,由大容量傳輸通道傳送到LED顯示屏現場,最終轉換成LED掃描控制信號,在LED顯示屏上實現高清晰的視頻、圖片、文本等節目內容的顯示。

1.1 顯示信號采集

本設計從電腦的DVI接口采集高清晰顯示數據信號。DVI主要基于轉換最小差分信號TMDS(Transition Minimizerl Differential signa-ling)技術來傳輸數字信號。TMDS運用編碼算法把8 tit(24位色RGB數據,每色各8 bit)通過最小轉換編碼轉換為10 bit數據(包含行場同步信息、時鐘信息、數據DE、糾錯等),并在DC平衡后,采用差分信號傳輸數據。它比LVDS、TTL具有更好的電磁兼容性能,可用低成本專用電纜實現長距離、高質量數字信號傳輸。本系統采用專用TFP401A芯片。將計算機顯示卡DVI接口輸出的TMDS信號轉換成TTL電平的RGB三色分離的數據信號。

1.2 顯示數據格式轉換

DVI接口高速輸入的顯示信號是串行含灰度的數據,以24位色數據為例,每個顏色的權值數據為8位,即灰度等級為256級(28)。LED顯示屏上的灰度實現,是通過控制每一個LED的點亮時間即占空比來實現的,為了更高效的實現不同的灰度,該設計采用全屏幕每個權值獨立顯示的方式,即控制整個屏幕分別顯示1~8個權值的亮度。

整個數據格式轉換過程由采集發送板和現場控制板上的2片FPGA以及數據緩存的SDRAM來實現。通過權值分離-緩存-分區提取-數據重整等一系列過程,最終得到LED顯示屏的掃描數據。

1.3 顯示數據傳送

DVI接口送過來的同步視頻信號數據量巨大。為了將大面積、高分辨率、高灰度的視頻顯示數據可靠的從電腦輸出到顯示屏體,需要采用可靠的傳輸媒介。另一方面,從計算機到LED顯示屏距離一般為幾十米到上百米。能傳輸的距離越長,從控制機房到顯示屏的距離限制越小,工程施工越靈活。

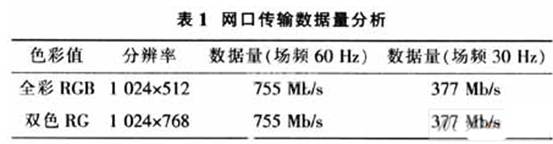

設計中的接口芯片采用RTL8208B實現。RTL8208B是Realtek公司生產的一款8口10 M/100 M以太網收發芯片。本設計中,采集發送板STR只需使用發送通道。現場控制板FRC同樣只需要接收通道。每根以太網網線含4對雙絞線,在百兆以太網中只使用到其中的2對,本設計中利用千兆以太網技術,使用全部4對雙絞線來作為傳送通道,這樣每根網線可傳輸400 Mb/s的數據量,2根網線(8路通道)可傳輸800 Mb/s的數據量。表l為網口傳輸數據量分析情況。其中,數據量=分辨率×場頻x256級灰度數據寬度。

從表l可以得到,單根網線可傳輸l 024x512全彩或者1 024x768雙色場頻30 Hz的數據;兩根網線傳輸l 024x512全彩或l 024x768雙色場頻60 Hz的數據。

1.4 LED顯示屏灰度掃描實現

LED顯示屏由多個顯示模組組合而成,顯示接口一般由以下幾個信號組成:串行數據信號:多組紅、綠、藍信號;串行時鐘信號;CLK;串行鎖存信號:LATCH;輸出使能信號:OE;行編碼信號(靜態模組時無行信號):一般最多16行掃描,行掃描信號在顯示屏模組上由譯碼器(74HCl38等)譯碼得到。

LED顯示屏為實現大面積顯示,屏幕面積一般非常巨大,而顯示屏的控制數據一般都是串行傳送,控制線都非常長且容易收到干擾,在大面積情況下可以保證穩定傳輸的信號頻率有限。如果增加系統的控制面積,一般方法有:1)提高顯示屏控制信號的時鐘頻率。但這種提高是有限的;2)降低刷新頻率。刷新頻率降低必將影響顯示穩定度,效果很差;3)多個控制器同時處理。增加掃描控制器必然增加成本。

本設計采用灰度切片的方式來實現高灰度、大面積、高刷新頻率顯示:按256級灰度(8位)計算,8位權值數據由高到低依次為D7(128權值),D6(64權值)……DO(1權值)。設置合適的輸出顯示屏的串行時鐘。提高并行輸出的RGB數據信號組,即可提高顯示屏面積并滿足實際高清顯示效果。本設計中,實際控制面積為l 024x768像素點。實際測試可以發現,采用灰度切片方式后,顯示屏亮度損失極小,可以實現非常穩定的視頻顯示。

2 系統設計

2.1 采樣發送板功能分解

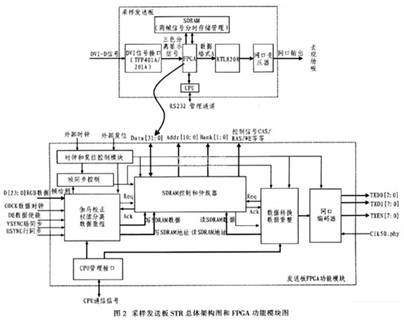

圖2為采樣發送板STR總體架構圖和FPGA功能模塊圖。

2.1.1 DVI接口

TFP40lA轉換后向FPGA輸入以下信號為QE/QO為每組信號送出紅綠藍各8 bit數據。本設計使用TFP40lA單鏈路TMDS方式;ODCK為數據時鐘;DE為數據使能;VSYNC/HSYNC為場同步信號,行同步信號。

2.1.2 STR核心控制FPGA設計

采集發送板的核心為高速邏輯器件FPGA,FPGA各功能框圖如圖2所示。FPGA通過實時采集數據并利用SDRAM緩存實現采樣、緩存、格式轉換等一系列高速同步數據處理。同時,FPGA通過采樣發送板上的CPU接收計算機的控制指令來適應不同的顯示屏和不同的應用環境。

FPGA各功能模塊說明如下:

1)采集模塊 ①伽馬校正:對于不同的節目源、不同的顯示屏體,需要經過不同數值的伽馬校正來獲得更符合人眼視覺的顯示效果,得到更清晰的圖像。本設計提供伽馬校正接口,通過采樣發送板上的MCU,可根據最終顯示效果設置不同的伽馬校正值。在采集數據輸入后,即轉換成經過校正的顯示數據。②權值分離和數據重組:對輸入串行數據進行權值分離處理,并根據CPU設置的顯示屏掃描模式進行初步數據重組。

2)SDRAM控制和仲裁器 系統需要實時處理每一幀顯示數據,通過大容量的外部存儲器作為緩存器。同步處理輸人幀接收和輸出幀提取。

在以往的設計中,一般采用2片SRAM(靜態存儲器)將2幀信號獨立存儲,大容量的SRAM成本高昂。本設計中。采用單片SDRAM設計。相同容量的SDRAM比SRAM價格低得多,而采用單片SDRAM,整個系統的成本將進一步下降;同時與FPGA接口減少,對FPGA的I/O口需求減少,優化器件選擇。

兩幀顯示信號分時讀寫,當前正在緩存的幀數據和當前正在讀取的上一幀數據在SDRAM里用不同的頁面來分別進行存儲。由于單片SDRAM控制和數據總線只有一組。所以需要SDRAM控制仲裁器模塊來實現無縫分時總線切換控制。

采集模塊和輸出模塊分別將數據流切片,轉成小數據塊,數據流切片后,各模塊每次占用總線的時間減短。經過精確計算每個模塊占用總線的時間、2次占用總線要求的最長間隔,設計合適大小的數據流切片大小:2個模塊即可實現無縫分時占用SDRAM總線。

3)網口編碼輸出 輸出控制模塊按照顯示屏的掃描模式分區采集緩沖SDRAM中的數據,并轉換重整成新的網口串行傳輸格式。除了顯示數據需要通過網口傳輸外,為實現遠程設置現場控制板,還需要將控制參數通過網口傳輸。網口編碼前將顯示數據包和控制信號包,經過分時復用,經網口編碼器編碼后送至RTL8208B傳送。

4)幀同步控制 數據在采樣發送板需要同步處理兩幀信號,為了穩定地將輸出網口的幀信號與輸入的DVI幀信號同步,幀同步模塊通過同步指令,將兩個時鐘域的幀信號鎖定在一起,以實現幀信號同步控制,避免出現顯示畫面斷裂的情況。

2.2 現場控制板功能分解

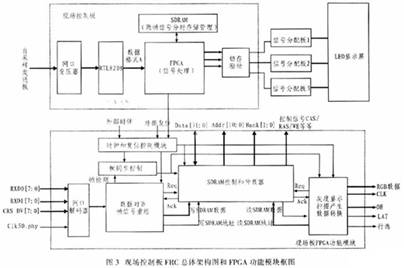

圖3為現場控制板FRC總體架構圖和FPGA功能模塊框圖。

2.2.1 FRC核心控制FPGA設計

現場掃描板的核心控制部分也為l片FPGA,FPGA通過實時接收網口數據并利用SDRAM緩存后,經過轉換,由輸出模塊實現灰度顯示,產生顯示屏的控制信號。各功能模塊說明如下:

1)網口解碼器和數據對齊、重整 現場掃描板的RTL8208B接收到網口送來的數據信號后送到FPGA的網口解碼器模塊。該模塊由狀態機實現:當依次檢測到DV信號、H信號、SSD信號后,解碼器開始定位并提取幀頭信號,根據幀頭碼中的數據類型判斷是控制幀還是數據幀,并分別進行提取。

2)SDRAM控制和仲裁器 同采集發送板類似,現場控制板的FPGA也需要需要實時處理每一幀顯示數據,通過大容量的外部存儲器SDRAM作為緩存器,同步處理輸入幀接收和輸出幀提取。SDRAM控制仲裁器模塊實現無縫分時控制。

3)灰度實現和掃描轉換 本模塊按照1.1節的描述,提取SDRAM中的各灰度數據,轉換成顯示屏的控制信號數據。根據采集發送板送來的控制幀中的掃描參數,調整掃描輸出的數據順序和控制信號格式,以方便實現對不同類型的LED顯示屏模塊組的靈活控制。LED灰度掃描輸出掃描仿真信號如圖4所示。

圖4為輸出原始信號圖,輸出信號再經過增加消影(行切換前關斷屏體,防止出現串行的暗影信號叫消影)、行調整、多顯示區穿插(控制更大面積)等處理后,經鎖存驅動后送到與顯示屏接口匹配的接口板,控制整個LED顯示屏屏體的顯示。

2.2.2 輸出驅動

輸出驅動將FPGA輸出的掃描信號鎖存驅動后送到輸出接口,外部再通過轉接板驅動后送至LED顯示屏。

3 結論

大規模邏輯具有處理速度快、容量大等特點,隨著技術的不斷更新,向著更高容量、更低單位成本的方向快速發展。在通信等實時系統等領域,系統設計中充分利用FPGA的特點,使用FPGA作為核心控制模塊,集成網絡控制、大容量存儲芯片控制、通信接口、外圍器件接口、信號采集接口等多個控制功能,能夠簡化系統架構、降低整個控制系統以及外圍成本;而精簡的系統架構,避免多個控制器件匹配而造成的系統失效率高、易相互干擾等缺陷。

系統設計中,充分考慮了技術的成熟性和整個系統工程的造價,本設計利用成熟的百兆網口芯片,靈活融入千兆網技術,令工程成本大為降低、而系統穩定性大幅提高。本控制系統在實際測試和應用中,無論是戶內還是戶外顯示屏,顯示穩定性和刷新頻率等參數均非常優秀,而且通過技術手段,大大增加了單系統控制的面積,降低了成本。通過與之配套開發的軟件同時使用,具有非常強的市場競爭力。