前 言

幾年前設(shè)計(jì)專用集成電路(ASIC) 還是少數(shù)集成電路設(shè)計(jì)工程師的事, 隨著硅的集成度不斷提高,百萬(wàn)門的ASIC 已不難實(shí)現(xiàn), 系統(tǒng)制造公司的設(shè)計(jì)人員正越來越多地采用ASIC 技術(shù)集成系統(tǒng)級(jí)功能(System L evel In tegrete - SL I) , 或稱片上系統(tǒng)(System on a ch ip ) , 但ASIC 設(shè)計(jì)能力跟不上制造能力的矛盾也日益突出。現(xiàn)在設(shè)計(jì)人員已不必全部用邏輯門去設(shè)計(jì)ASIC, 類似于用集成電路( IC) 芯片在印制板上的設(shè)計(jì),ASIC 設(shè)計(jì)人員可以應(yīng)用等效于印制板上IC 芯片的功能模塊, 稱為核(core)、或知識(shí)產(chǎn)權(quán)( IP) 宏單元進(jìn)行系統(tǒng)設(shè)計(jì), 這就是基于核的設(shè)計(jì)方法。CPU、存儲(chǔ)器、總線控制器、接口電路、DSP 等都可成為核。但是ASIC 設(shè)計(jì)與印制板(PCB) 設(shè)計(jì)有很大區(qū)別,ASIC 必須用EDA 工具進(jìn)行硬件設(shè)計(jì), 主要問題都是通過計(jì)算機(jī)仿真解決, 而不能象印制板設(shè)計(jì)那樣通過實(shí)驗(yàn)調(diào)試解決, 另外ASIC 的制造還需要數(shù)量可觀(一般數(shù)萬(wàn)美元) 的不可重復(fù)工程費(fèi)用(NRE)。80年代后期出現(xiàn)的現(xiàn)場(chǎng)可編程門陣列(FPGA" title="FPGA">FPGA ) 和復(fù)雜可編程邏輯器件(CPLD) 是ASIC 的一種, 其優(yōu)點(diǎn)是在制造廠家提供的FPGA 或CPLD 芯片上, 可由設(shè)計(jì)工程師對(duì)其進(jìn)行現(xiàn)場(chǎng)編程完成ASIC 的最后設(shè)計(jì), 而不需昂貴的NRE 費(fèi)。現(xiàn)在FPGA 的規(guī)模已達(dá)到百萬(wàn)門, 如XILINX 公司的V irtex 系列, 完全可以實(shí)現(xiàn)片上系統(tǒng),其設(shè)計(jì)方法將逐步轉(zhuǎn)向核基設(shè)計(jì)。

1 核的分類和特點(diǎn)

核是一種預(yù)定義的并經(jīng)過驗(yàn)證的復(fù)雜功能模塊, 它可以集成到系統(tǒng)設(shè)計(jì)中。核基設(shè)計(jì)主要特點(diǎn)是可重復(fù)使用已有設(shè)計(jì)模塊, 縮短設(shè)計(jì)時(shí)間, 減少設(shè)計(jì)風(fēng)險(xiǎn), 通過高層的集成可望提高整個(gè)系統(tǒng)的性能。在FPGA 設(shè)計(jì)中的核分為三種, 如表1所示:

表1 核的分類和特點(diǎn)

硬核

(hard core)

預(yù)定義的已布局布線的模塊 不能修改設(shè)計(jì), 必須采指定實(shí)現(xiàn)技術(shù) 時(shí)序性能有保證

固核

(firm core) HDL 源碼,與實(shí)現(xiàn)技術(shù)有關(guān)的網(wǎng)表 部分功能可以修改, 采用指定的實(shí)現(xiàn)技術(shù) 關(guān)鍵路徑時(shí)序可控制

軟件

(soft core)

行為級(jí)或RTL 級(jí)HDL源碼 可修改設(shè)計(jì),與具體實(shí)現(xiàn)技術(shù)無關(guān) 時(shí)序性能無保證, 由使用者確定

硬核是針對(duì)特定的實(shí)現(xiàn)技術(shù)優(yōu)化的, 它具有不能修改的結(jié)構(gòu)和布局布線, 可作為庫(kù)元件使用, 且時(shí)序性能穩(wěn)定, 但硬核不能按設(shè)計(jì)需要修改和調(diào)整時(shí)序。固核由HDL 源碼和與實(shí)現(xiàn)技術(shù)有關(guān)的網(wǎng)表組成, 使用者可按規(guī)定增減部分功能。固核的關(guān)鍵路徑時(shí)序是固定的, 但其實(shí)現(xiàn)技術(shù)不能更改, 即不同廠家FPGA 的固核不能互換使用。軟核是可綜合的硬件描述語(yǔ)言(HDL ) 源碼, 它與實(shí)現(xiàn)技術(shù)無關(guān), 可按使用者需要修改, 具有最大的使用靈活性, 但軟核的關(guān)鍵路徑時(shí)序性能無保證, 最終性能主要決定于使用者采用的綜合、布局布線和實(shí)現(xiàn)技術(shù)。

在FPGA 設(shè)計(jì)中, 由于不同廠家的具體實(shí)現(xiàn)技術(shù)差別較大, 完全與硬件實(shí)現(xiàn)技術(shù)無關(guān)的軟核性能受到很大限制, 而硬核缺少使用的靈活性, 因此作為軟、硬核折中的固核使用較多。以上是具有代表性的核的分類, 在實(shí)際使用中, 某種功能的核往往以各種形式出現(xiàn), 由使用者按需要選用, 軟核也不僅只有HDL 源碼, 還包括用于功能測(cè)試的行為模型和測(cè)試向量, 用于指導(dǎo)綜合的約束文件。

2 核基FPGA 設(shè)計(jì)方法簡(jiǎn)介

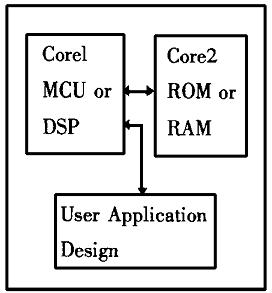

在核基設(shè)計(jì)中, 一個(gè)完整的設(shè)計(jì)主要由兩部分組成, 一部分是核, 如圖1中的MCU、RAM , 另一部分是用戶自己定義的邏輯電路。按系統(tǒng)設(shè)計(jì)的要求將這些功能模塊連接在一起就完成了芯片的設(shè)計(jì),各個(gè)核或功能塊的連接目前還沒有統(tǒng)一的標(biāo)準(zhǔn), 因不同的設(shè)計(jì)而定, 一般應(yīng)滿足一定的時(shí)序要求。作為核基設(shè)計(jì)的第一步是選擇合適的核, 這主要從核的功能、性能可靠性和實(shí)現(xiàn)技術(shù)幾方面來選擇。

圖1 核基設(shè)計(jì)芯片示意圖

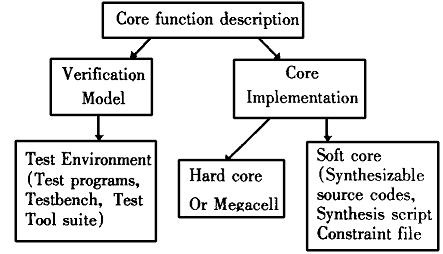

一個(gè)核首先要有核的功能描述文件, 用于說明該核的功能、時(shí)序要求等, 如圖2所示, 其次還要包括設(shè)計(jì)實(shí)現(xiàn)和設(shè)計(jì)驗(yàn)證兩個(gè)方面的文件, 即不但要有實(shí)現(xiàn)核功能的寄存器傳輸級(jí)(RTL ) 源碼或網(wǎng)表, 還要有用于核實(shí)現(xiàn)后驗(yàn)證邏輯功能正確性的仿真模型和測(cè)試向量。硬核的實(shí)現(xiàn)較簡(jiǎn)單, 類似于PCB 設(shè)計(jì)中IC 芯片的使用, 軟核的使用情況較為復(fù)雜, 實(shí)現(xiàn)后的性能與使用者的具體實(shí)現(xiàn)方式有關(guān), 為保證軟核的性能, 軟核提供者一般還提供綜合描述文件, 用于指導(dǎo)軟核的綜合, 固核的使用介于上述二者之間。

圖2 核由設(shè)計(jì)實(shí)現(xiàn)和設(shè)計(jì)驗(yàn)證組成

很多核提供者都提供核的評(píng)價(jià)環(huán)境和演示、開發(fā)板,便于用戶了解核的功能和使用。

核基FPGA 設(shè)計(jì)流程如圖3所示。設(shè)計(jì)輸入部分包括:

1) 用戶設(shè)計(jì)邏輯、軟核、固核或硬核仿真模型的輸入,

2) 功能仿真,

3) 邏輯綜合。其中仿真模型是一個(gè)行為級(jí)模型, 只用作功能仿真, 不進(jìn)行綜合。

圖3 核基FPGA 設(shè)計(jì)流程

設(shè)計(jì)的輸入一般是采用HDL 語(yǔ)言, 如VHDL、V erilog 等, 輸入完設(shè)計(jì)和仿真模型后就可進(jìn)行功能仿真, 當(dāng)功能仿真完成后, 就可進(jìn)行邏輯電路的綜合。

用戶邏輯和軟核的綜合應(yīng)加合理的時(shí)序約束, 以滿足設(shè)計(jì)的要求, 約束條件可由綜合文件(Synthesis Script ) 給出。完成設(shè)計(jì)輸入后進(jìn)入設(shè)計(jì)實(shí)現(xiàn)階段,在此階段固核的網(wǎng)表和設(shè)計(jì)約束文件, 用戶綜合出的網(wǎng)表和設(shè)計(jì)約束文件一起輸入給FPGA 布局布線工具, 完成FPGA 的最后實(shí)現(xiàn), 并產(chǎn)生時(shí)序文件用于時(shí)序仿真和功能驗(yàn)證。最后進(jìn)入設(shè)計(jì)驗(yàn)證階段,用靜態(tài)時(shí)序分析判定設(shè)計(jì)是否達(dá)到性能要求, 對(duì)比功能仿真結(jié)果和時(shí)序仿真結(jié)果, 驗(yàn)證設(shè)計(jì)的時(shí)序和功能是否正確。若設(shè)計(jì)的性能不能達(dá)到要求, 需找出影響性能的關(guān)鍵路徑, 并返回延時(shí)信息, 修改約束文件, 對(duì)設(shè)計(jì)進(jìn)行重新綜合和布局布線, 如此重復(fù)多次直到滿足設(shè)計(jì)要求

為止。若重復(fù)多次還不能達(dá)到設(shè)計(jì)要求, 則需修改設(shè)計(jì)或采用其它實(shí)現(xiàn)技術(shù)。

3 軟核的設(shè)計(jì)及使用

由于FPGA 的硬件技術(shù)迅速發(fā)展, 硬件資源越來越豐富, 速度越來越快, 使軟核資源利用率不高、工作速度較低等不足得到很大的彌補(bǔ), 軟核在核基設(shè)計(jì)中作用越來越大。其主要優(yōu)點(diǎn)是功能與實(shí)現(xiàn)技術(shù)無關(guān), 使用靈活。這樣我們可以很方便地在不同的實(shí)現(xiàn)技術(shù)下使用軟核。如用X IL INX FPGA 實(shí)現(xiàn)的軟核, 不需改動(dòng)設(shè)計(jì), 重新綜合后就可以用ACTEL FPGA 實(shí)現(xiàn), 設(shè)計(jì)實(shí)現(xiàn)的靈活性大為提高。但軟核的性能受實(shí)現(xiàn)技術(shù)影響還是很大, 怎樣保證軟核達(dá)到預(yù)想的性能是目前需要解決的難題。國(guó)外近年提出了與實(shí)現(xiàn)技術(shù)無關(guān)的可綜合軟核的思想, 希望通過對(duì)編制軟核的HDL 源碼的某種限制, 并結(jié)合綜合工具的時(shí)序約束功能, 達(dá)到部分控制軟核性能的目的。如限制軟核只能采用嚴(yán)格的同步邏輯設(shè)計(jì), 沒有反饋環(huán)路、多時(shí)鐘路徑、三態(tài)邏輯、鎖存器和異步置位復(fù)位觸發(fā)器, 只使用D 觸發(fā)器和邏輯門。這樣借助于綜合工具, 可有效地控制軟核關(guān)鍵路徑的延時(shí),并預(yù)測(cè)具體實(shí)現(xiàn)技術(shù)中軟核的性能。當(dāng)然這是以犧牲一定的FPGA 邏輯資源為代價(jià)的, 但隨著硅技術(shù)的發(fā)展, 硬件資源十分豐富, 用一定的硬件資源浪費(fèi)去換取設(shè)計(jì)靈活性提高是值得的, 正如在PC 機(jī)軟件設(shè)計(jì)中, 現(xiàn)在已很少有人過多考慮程序占用的存儲(chǔ)空間一樣。

本文作者按照上述軟核設(shè)計(jì)思想, 采用全同步邏輯設(shè)計(jì), 只使用D 觸發(fā)器和邏輯門, 實(shí)現(xiàn)了與PIC16C57兼容的8位微控制器的設(shè)計(jì)。頂層結(jié)構(gòu)如圖4, 采用哈佛結(jié)構(gòu), 取指和指令執(zhí)行并行工作, 除少數(shù)幾條程序跳轉(zhuǎn)指令外, 全部為單時(shí)鐘周期指令。程序存儲(chǔ)器ROM 一般放在FPGA 外, 若ROM 中指令較少, 也可放在FPGA 內(nèi)。數(shù)據(jù)總線采用多路選擇器形式, 以適應(yīng)不同的實(shí)現(xiàn)技術(shù)。指令寄存器和特殊功能寄存器, 包括IO 端口寄存器、狀態(tài)寄存器、程序計(jì)數(shù)器等, 都由D 觸發(fā)器構(gòu)成, 通用寄存器采用了FPGA 的RAM 模塊, 指令譯碼和算數(shù)邏輯單元由組合邏輯門構(gòu)成。

圖4 8位微控制器頂層結(jié)構(gòu)圖

實(shí)現(xiàn)的主要功能:

(1) 指令與P IC16C57兼容。

(2) 三個(gè)8位雙向IO 口。

(3) 程序存儲(chǔ)器2K X 12 B IT。

(4) 內(nèi)部RAM 共32個(gè), 7個(gè)為特殊寄存器。

(5) 二級(jí)子程序堆棧。

(6) 未實(shí)現(xiàn)指令: POT ION、SLEEP、CLRWDT。

(7) 單相時(shí)鐘。

該軟核用VHDL 語(yǔ)言完成設(shè)計(jì)的輸入, 用EXPRESS 綜合工具進(jìn)行綜合, 采用Xilinx 4000系列FPGA 實(shí)現(xiàn), 不包括ROM 約需2500邏輯門, 時(shí)鐘頻率5MHz, 即運(yùn)行一條指令200ns。

上述軟核在綜合、布局布線時(shí), 只給予了簡(jiǎn)單的時(shí)序約束, 當(dāng)需要改用其它FPGA 實(shí)現(xiàn)時(shí), 可用綜合工具重新綜合、布局布線, 一般不需改變時(shí)序約束文件就能達(dá)到上述性能, 因此當(dāng)時(shí)鐘頻率不太高時(shí),軟核的使用還是較為方便的。但當(dāng)時(shí)鐘頻率較高時(shí),雖然采用了與實(shí)現(xiàn)技術(shù)無關(guān)的可綜合軟核的思想,軟核的性能還是與使用者及其采用的實(shí)現(xiàn)技術(shù)緊密相關(guān), 要真正做到與實(shí)現(xiàn)技術(shù)無關(guān)是很困難的。此時(shí)軟核的使用者必須清楚其使用的復(fù)雜性, 最好能得到軟核提供者的技術(shù)支持, 許多軟核提供者都提供這方面的服務(wù)。

4 總結(jié)

隨著硅技術(shù)的發(fā)展, 集成電路芯片的硬件生產(chǎn)能力迅速提高, 幾年前FPGA、CPLD 的規(guī)模還在萬(wàn)門左右, 現(xiàn)在ALTERA 公司已宣布將推出250萬(wàn)門的CPLD。如此快的發(fā)展速度, 使集成電路設(shè)計(jì)能力嚴(yán)重不足, 只靠增加設(shè)計(jì)人員, 不從設(shè)計(jì)方法上改進(jìn), 提高設(shè)計(jì)的效率, 是不可能解決問題的。因此基于核的設(shè)計(jì)、設(shè)計(jì)重利用等技術(shù), 近年來在國(guó)外發(fā)展很快, 并成立了相應(yīng)的標(biāo)準(zhǔn)化組織, 如VSIA (Virtual Socket Interface Alliance) , 專門從事核或稱IP模塊的互連標(biāo)準(zhǔn)研究, 以使核的使用就象在印制板上使用集成電路塊一樣方便。一個(gè)片上系統(tǒng)的時(shí)代即將到來, 電子工程師應(yīng)跟上這個(gè)時(shí)代發(fā)展的潮流,正如以前電子管系統(tǒng)向晶體管系統(tǒng), 分離元件系統(tǒng)向集成電路系統(tǒng)發(fā)展一樣。