中文引用格式: 方勝利,孫航,李煒,等. Virtuoso Schematic Migration在模擬電路遷移中的應用[J]. 電子技術應用,2025,51(8):11-15.

英文引用格式: Fang Shengli,Sun Hang,Li Wei,et al. Application of VSM in analog circuit migration[J]. Application of Electronic Technique,2025,51(8):11-15.

引言

在現代電子設計領域,原理圖是硬件開發的基石,它不僅是電路設計的藍圖,更是連接概念與實物的橋梁。然而,隨著技術迭代加速、工具鏈演進和行業需求變化,原理圖遷移逐漸成為工程師與設計團隊無法回避的關鍵任務。這一過程涉及將現有電路設計從舊版EDA(電子設計自動化)工具或環境遷移至新平臺,其復雜性遠超簡單的格式轉換,而是涵蓋數據兼容性、設計完整性、團隊協作和長期戰略價值的綜合工程[1]。在EDA領域,原理圖遷移是設計團隊在工具升級、技術迭代或協作需求下不可避免的關鍵環節。隨著半導體工藝進步、設計復雜度提升以及行業標準演進,傳統的EDA工具可能無法滿足現代設計需求,促使企業將舊版原理圖遷移至更先進的平臺。然而,這一過程并非簡單的文件格式轉換,而是涉及符號庫匹配、網絡連接驗證、設計規則適配等一系列技術挑戰,稍有不慎便可能導致設計功能變異、生產延誤甚至成本超支[2]。

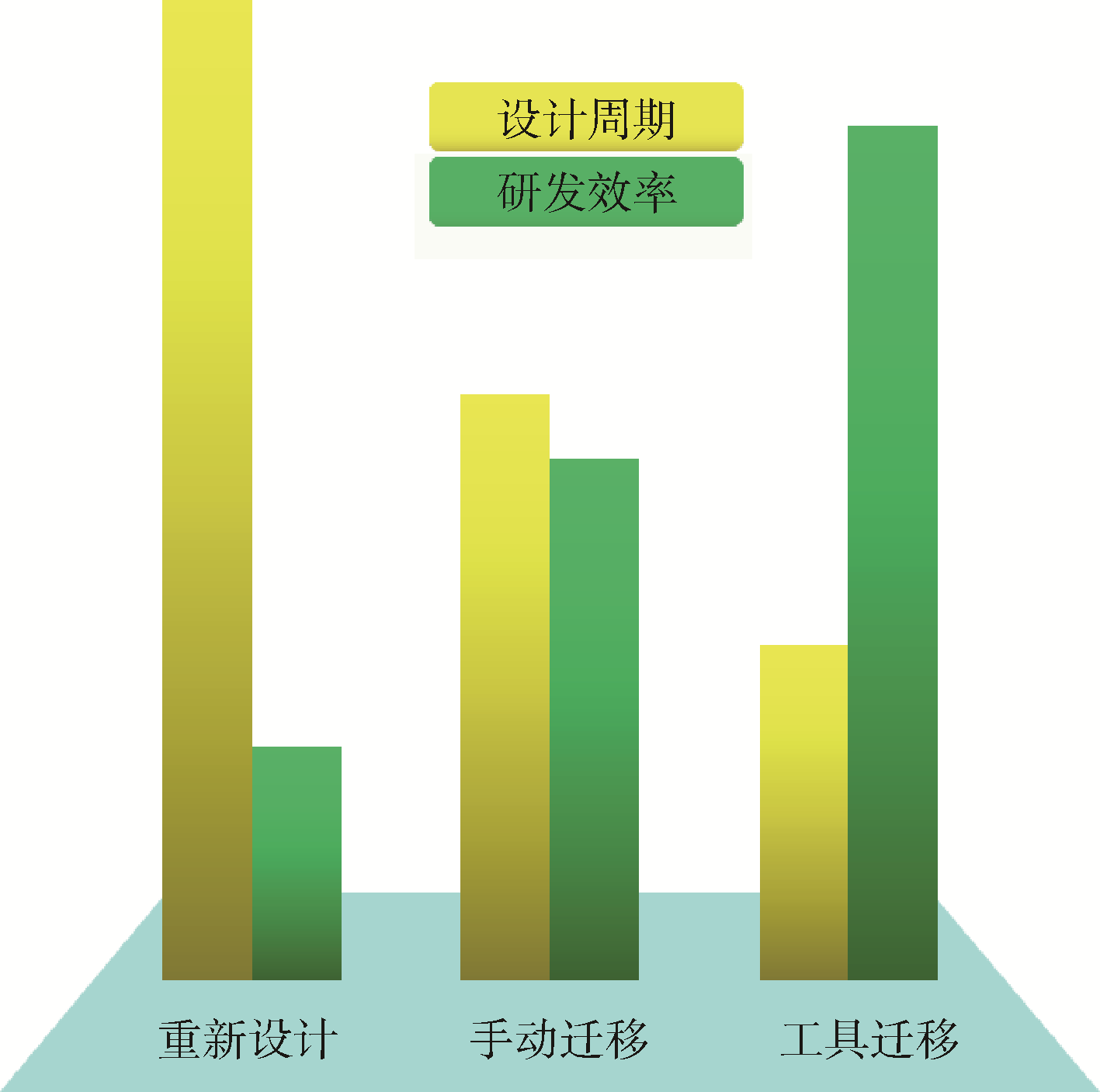

原理圖遷移在芯片設計中變得越來越重要。如圖1所示,首先,原理圖遷移可以縮短設計周期,加速上市時間。遷移時可重用原有電路的架構、IP核和成熟模塊,減少重新設計的時間。已有功能邏輯和測試用例可直接適配,減少驗證和調試周期。現代EDA工具支持自動化遷移(如工藝庫替換、布局優化),提升效率。其次,降低開發成本與風險減少研發投入。相比從零設計,遷移節省人力、流片和驗證成本。原有電路已通過市場驗證,工藝遷移主要解決物理實現問題,而非功能缺陷。避免全新設計可能存在的架構缺陷或性能不達預期的問題。優勢在于快速響應工藝升級或供應鏈需求,但需注意模擬電路的敏感特性(如匹配、寄生效應),通常需人工干預優化。此外,當前原理圖遷移仍然存在一些需要逐步攻克的難題。例如,如何確保遷移前后的器件參數一致,如何確保porting前后器件symbol尺寸不同時能夠連線正確等問題。

盡管存在困難,成功的原理圖遷移能顯著提升設計效率、降低長期維護成本,并確保知識資產的可持續利用。近期Cadence在Virtuoso Studio IC23.1中基于Schematic XL開發出先進的電路遷移平臺Virtuoso Schematic Migration(VSM),該工具不僅支持多個library之前的協同遷移,同時也支持電路頂層的hierarchy遷移,在不同晶圓廠商工藝間遷移時也能自動解決器件pin錯位的問題。此外,Cadence近期推出的device mapping GUI將之前繁雜的mapping規則手動編寫改成了用戶界面點擊的方式,大幅提高了mapping file 的準確性,同時也大幅提升了整個遷移流程的效率。綜上,前端工程師可以利用migration實現更多工作,大幅度提高工作效率,縮短項目交付周期。

本文針對本公司一些實際的電路,基于該工具實現了在不同工藝間的遷移,大大提高了相同電路不同工藝間的復用效率,很大程度節省電路設計工程師對電路手動遷移所花費的時間。綜上,工程師可以利用VSM來加速提高工作效率,縮短項目交付周期。

圖1 原理圖遷移中涉及周期和研發效率的對比關系

本文詳細內容請下載:

http://www.jysgc.com/resource/share/2000006621

作者信息:

方勝利1,孫航1,李煒1,丁學偉1,凌秋嬋2

(1.深圳市中興微電子技術有限公司,廣東 深圳 518055;

2.楷登電子科技有限公司,上海 200120)