大家好,我是來自印度卡納塔克邦國立技術學院的高級EE本科生Shivam Potdar。大約一年前,我通過CS61C和UC Berkeley的課程內容接觸到了RISC-V 。然后,我有機會作為自由和開源硅基金會(FOSSi)的Google Summer of Code(GSoC)學生,探索幾種新穎的技術,這些技術與RISC-V一起將塑造我們的未來行業。現在,它已成為知識和探索的永無止境的旅程。

我是Shivam Potdar,來自印度卡納塔克國立理工學院的EE大四學生。大約一年前,通過加州大學伯克利分校CS61C的課程內容,我接觸到了RISC-V。

然后,我得到了一個機會,作為自由和開源硅基金會(FOSSi)的Google Summer of Code (GSoC)學生,探索了幾項新技術,這些技術加上RISC-V,將塑造我們行業的未來。現在,它已經變成了一個永無止境的知識和探索之旅。

GSoC是谷歌資助的一個項目,鼓勵學生為開源項目做貢獻。由于RISC-V的成立以及FOSSi、lowRISC、Symbiflow、BeagleBoard.org等組織,開源硬件項目的參與度越來越高。

RISC-V最令人興奮的一個方面是它為多個領域的新想法提供了一個開放的場所。它已經成為OpenTitan等架構創新的首選,也成為展示諸如Chisel(Rocket芯片、SiFive內核)、SpinalHDL(VexRiscv)、BlueSpec(Shakti處理器)等新HDL的首選。

以下是我在這個暑假期間所作的一些探索:

用TL-Verilog進行事務級建模

使用Makerchip輕松進行設計和調試

開源硬件和免費提供的設計工具

開源形式驗證

異構的ISA多核平臺

我致力于增強一個名為WARP-V的RISC-V內核,采用TL-Verilog的前瞻性設計方法,并與OpenPiton(一個用SystemVerilog編寫的開源多核框架)集成。

TL-Verilog是對SystemVerilog的革命性擴展,由我的GSoC導師Steve Hoover領導。它在事務層面對系統進行建模,具有時序抽象、高度可參數化、靈活、易學習/調試/文檔的特點,并顯著減少了代碼大小。它既不是HLS,也不是應用于硬件的編程語言,而是一個具有現代特征的抽象,使建模非常接近硬件。

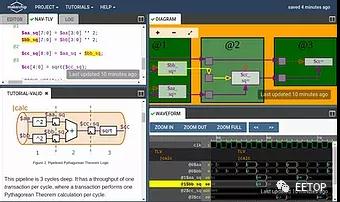

Makerchip.com是一個免費的基于Web的TL-Verilog集成開發環境,它支持設計、調試、仿真和Verilog轉譯都在瀏覽器標簽中完成!WARP-V主要是在這個平臺上開發的。SandPiper是TL-Verilog的編譯器,將其翻譯成可綜合的(System)Verilog,與開放源代碼和經過行業驗證的設計流程兼容。

在學校里,我花了幾個星期的時間進行設計和調試,才用Verilog / VHDL完成了一個基本的MIPS實現。另一方面,我是由Steve和Kunal Ghosh組織的“RISC-V 30小時內為你服務(MYTH)”研討會的中的助教。大約有200名參與者,其中許多人沒有數字設計的背景,他們學習了RISC-V,并在短短五天內為社區貢獻了35個TL-Verilog核。我將在10月8日的VSDOpen 2020上再次幫助舉辦類似的研討會,該研討會將在1.5小時內來介紹TL-Verilog!

WARP-V在TL-Verilog中提供了一個高度可配置的CPU,支持各種流水線深度,WARP-V在TL-Verilog中呈現了一個高度可配置的CPU,支持各種流水線深度、長延遲指令、分支預測、時鐘門控、內聯匯編器,甚至是多個ISA! 對于RISC-V,內核支持RV32I[M][F],也通過了riscv-formal的正式驗證。它還使用Steve的定制邏輯即服務項目--1st CLaaS在AWS FPGA上進行了表征和測試。對于RISC-V,內核支持RV32I [M] [F],該產品也已通過riscv-formal進行了正式驗證。還使用Steve的定制邏輯即服務項目1st CLaaS在AWS FPGA上對它進行了仿真和測試。

OpenPiton是一個多核研究平臺,通過向內核提供內存子系統、IO接口、緩存和共享資源來支持異構ISA。它兼容SPARC、RISC-V和x86,以及已有的幾種外設。

暑假期間,我致力于在WARP-V中添加RISC-V M型擴展,對其進行正式驗證,并通過支持長等待時間指令并提供外部存儲器接口來為OpenPiton集成做準備。

在過去的幾個月里,我可以觀察到RISC-V的巨大增長速度。這個生態系統是如此的開放和包容,以至于我今天成為了RISC-V國際的社區成員,并參與各種在線聚會、網絡研討會和全球論壇等活動。

今天,我們可以通過Symbiflow、Openlane、Yosys、Verilator和Skywater PDK等FOSS工具來執行整個RTL到GDS的流程,包括FPGA仿真、模擬和制造。這些工具和技術(如TL-Verilog與RISC-V搭配)所支持的現代方法論確實將改變半導體產業。

有人恰當地將RISC-V表示為硬件的Linux。令人振奮的是,看到硬件的民主化和行業變化的動態,如今,即使是無晶圓廠的初創企業也可以與老牌巨頭競爭。作為一名即將進入該領域的學生,RISC-V的前景一片光明。

看了以上內容,總感覺和前一段時間刷屏的國科大本科生RISC-V流片的不太一樣,感覺到我們更加偏重于應用實現,而這個印度學生所作的更像是在做更多的研究與探索。雖然沒有流片,但是總體來說這個印度本科生所做的并不比我們差。