潘澤鍇,蘭國莉

(廣西職業技術學院 計算機與電子信息工程系,廣西 南寧 530226)

摘要:采用DDS技術設計工業控制現場測試信號源,基于VHDL語言進行系統建模,對DDS進行重新參數設計,實現IP核重構,能夠根據需要修改參數以實現器件的通用性;利用QuartusⅡ平臺完成具體DDS芯片設計,闡述了基于VHDL編程的DDS設計的方法步驟。經測試,該設計各項設計指標符合要求,具有很好的實用價值。

中圖分類號:TN914文獻標識碼:ADOI: 10.19358/j.issn.16747720.2016.23.023

引用格式:潘澤鍇,蘭國莉. DDS工業數字移相信號發生器應用設計[J].微型機與應用,2016,35(23):80-82.

0引言

直接數字頻率合成信號發生器(Direct Digital Synthesize,DDS)具有易產生、分辨率高、絕對誤差小等優點,在已有電子系統及設備的頻率設計中,以及在工業控制現場信號測試中得到越來越廣泛的應用[1]。在進行工業現場通信信號的傳輸測試實驗中,在原有信號發生器攜帶不方便、輸出不穩定的情況下,以DDS技術為基礎設計新型信號發生器,利用VHD語言實現對DDS功能的重新設計,可以簡單地完成在不同方式下的移植,輸出參數可以根據現場環境進行適當的修改[2]。在實現過程中使用Alter公司開發的QuartusⅡ軟件,該軟件不僅提供了VHDL開發編譯環境,還集成了DDS設計開發所需要的FPGA器件,這樣就可以大大降低開發難度和縮短開發周期[3]。

1DDS原理及系統分析

DDS是一種全數字、高分辨精度、反應速度在毫微秒量級的頻率合成技術,屬于開環無反饋環節的控制系統結構。根據它的相位特性可知其相位是連續變化的,而且相位誤差極小,可以輸出很好的頻譜波形,一些在傳統的頻率合成困難的情況下使用DDS技術可以很好地完成[4]。

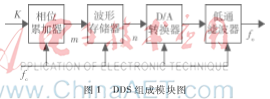

分析直接數字頻率合成原理,利用QuartusII軟件,基于FPGA配合相應外圍器件實現多波形信號發生器,電路結構簡單、易于擴展,具有極大的靈活性和方便性。由圖1可知,DDS波形發生器由相位累加器、波形存儲器、D/A轉換器和低通濾波器4個模塊組成[5]。

由圖1的DDS組成模塊圖可知DDS信號發生器的工作原理:在每次接收到一個時鐘脈沖fc時,頻率控制字K和相位累加器兩者之間相位數據相互累加,累加結果送累加寄存器保存,相位累加器由N位加法器與N位累加寄存器級聯組成,將獲得的累加器脈沖再反饋回去與原來累加的新接收到的下一個時鐘脈沖相加,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字相加,不斷對相位進行累加獲得輸出脈沖。這就相當于,相位累加器在每一個脈沖到來的時候都實現脈沖累加,最后的脈沖輸出就是脈沖不斷累加的結果。累加輸出的頻率就是合成以后DDS信號輸出的頻率,相位累加器輸出的數據作為波形存儲器ROM的相位取樣地址,通過查表的方式可以獲得波形信號取樣,完成相位到幅值的轉換[6]。

累加器通過相位累加的方式實現脈沖輸出之后放于波形存儲器,波形存儲器的輸出送到D/A轉換器,D/A轉換器的主要作用就是把輸出波形的數字信號變成模擬信號,完成所需要的信號形式,但是輸出的信號可能含有毛刺,可以通過低通濾波器的方式去除毛刺和其他諧波,最后輸出一個合成頻率為f0的信號波形[7]。輸出頻率f0與時鐘頻率fc之間的關系滿足下式:

由公式(1)可知,輸出的頻率f0是時鐘脈沖fc與頻率控制字K合成的結果,同時還與位數N有關,通過改變K值可以改變頻率的輸出。DDS信號發生器輸出的最小頻率可以由方程△f= f0/2N確定。頻率分辨率在fc固定時,取決于相位累加器的位數N。只要N足夠大,理論上就可以獲得足夠高的頻率分辨精度。另外,由采樣定理,合成信號的頻率不能超過時鐘頻率的一半,即f0≤fc/2,因此頻率控制字的最大值Kmax應滿足Kmax≤2N-1。

在FPGA內部比較容易產生信號生成模塊,而單純的DDS芯片不但價格高,而且功耗大,在這方面使用FPGA技術就有很大的優勢。鑒于此,本設計采用FPGA技術產生DDS信號發生器來實現任意波形發生器的設計。

2DDS設計與實現

2.1DDS波形發生器總體設計

根據DDS的基本原理及系統分析,可以比較具體地設計出整個波形發生器的總體方案,如圖2所示。

根據設計的波形發生器的原理圖,在設計中需要對重現信號波形進行周期性取樣作為參考波形,DDS控制器根據參考波形設定頻率參數,和需要選擇的輸出波形參數存儲在波形RAM單元中;根據待設波形進行幅度設定,把頻率設定參數和經過幅度變換后的波形進行線性疊加后經D/A轉換輸出信號波形[4]。

本設計中調用LPM即參數可設置模塊庫來生成存儲器模塊。在設計波形信號發生器的過程中,如果要使用FPGA特定的器件,那么在設計VHDL程序中亦要使用與該期間配套的宏模塊功能,而這些在軟件使用中可以以圖形或是硬件語言描述的形式來實現,可大大提高設計的效率和可靠性[5]。

2.2系統FPGA設計實現

利用FPGA實現雙DDS 的相位累加器,通過數字方法實現頻率調制,通過查表的方式,DDS利用RAM操作總線與FPGA內部CPU通信,實現各種波形[6]。實現的基本原理如圖3所示。

在實際測試中以正弦波為例,系統采用QuartusII軟件進行設計,使用GW48 EDA/SOPC實驗開發平臺進行調試,系統分為波形數據ROM模塊、32位加法器模塊、32位寄存器模塊、10位加法器模塊、10位寄存器模塊等幾部分[7]。

2.3用戶控制

系統使用實驗開發平臺的鍵盤和LED接口實現人機交互,通過鍵盤設定待輸出的波形、波形的頻率以及波形的幅度等參數。

待輸出波形部分使用了3個按鍵,每個按鍵對應一種波形,對應的發光二極管顯示有效狀態,并且可以多個按鍵同時起作用,此時即波形的線形疊加,該功能的實現是通過使能對應的波形數據ROM的輸出和幅值控制的輸出實現的[8]。

頻率調節使用了一個雙向計數器給DDS控制器賦值來控制輸出信號的頻率(周期輸出點數),其中雙向計數器有一個輸入端控制計數方向,即加還是減,另一個進行計數。該部分設計受實驗臺的限制(按減少)不能直接輸入數字,因此設定比較慢,而頻率設定的具體數值在實驗臺上可使用兩位數碼管來顯示。

設計的相位累加器對于每來一個時鐘脈沖加法器就會與累加寄存器的累加相位相加,在一個時鐘作用之后,加法器的輸入端又會加入新的相位數據,與上一個時鐘周期的相位進行累加。當相位累加器加滿之后會溢出,實驗中以相鄰兩次累加器溢出時間間隔為一個周期合成DDS信號,而在每次信號合成的取數環節之前,會在累加器輸出的信號加上相位移,以此來對相位進行調節[9] 。

因為幅值分別對應3種不同類型的波形,因此需要對其分別設定,該部分共使用了3個按鍵,其中一個按鍵用來設定待調節幅值的波形,直接使用一加計數器,通過實驗平臺上的輸出發光二極管來顯示所選定的波形。幅值大小的調整同頻率調整,使用了雙向計數器,調整的輸出由乘除器進行變換后輸出[10]。設定波形幅度的數值顯示在實驗臺的LED數碼管上,每個波形幅值顯示使用兩位LED數碼管,供使用6個。

3功能測試與結果輸出

使用QuartusII任意生成一個1 024單元10 bit寬的mif文件,將其中的信息拷入到sin_rom.mif中,最后將生成的sin_rom.mif加入到LPM_ROM中去[7]。QuartusII提供了強大、直觀、便捷和操作靈活的原理圖輸出設計功能,本實驗輸出的原理圖如圖4。

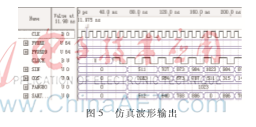

利用FPGA設計DDS信號發生器后使用QuartusII進行時序仿真,設置好相應的仿真參數,得出的仿真波形如圖5所示。

使用QuartusII自帶的Signal tap邏輯分析儀進行硬仿真測試,為了能對此信號進行硬件測試,將芯片固定的端口與輸入輸出信號綁定,通過軟件編譯好之后下載到硬件進行測試。

在測試完成之后,重新對配置芯片進行編程,最終完成信號發生器信號的輸出。圖6、圖7是在相同條件下不同頻率的正弦波對應的邏輯分析儀采樣結果。

通過測試表明,設計的DDS數字移相信號發生器具有連續輸出正弦波波形的功能,使用鍵盤輸入具有產生周期性先行組合波形的能力,輸出波形的頻率范圍在100 Hz~200 kHz,且頻率步進間隔≤100 Hz,具有顯示輸出波形的類型、重復頻率(周期)和幅度的功能。

4結論

采用FPGA器件,利用VHDL語言對DDS信號發生器進行重新設計與實現,可以在不同的方式下進行移植和參數修改,信號發生器輸出信號穩定,便于攜帶。通過測試表明各項設計指標符合要求,具有很好的實用價值。

參考文獻

[1] 丁革媛, 李振江,宋揚,等. 工業控制系統中的安全隱患分析[J].微型機與應用,2015,34(1):7-9.

[2] 白麗娜,周渭,趙桀,等. 一種和DDS結合的高分辨率頻率計設計[J].西安電子科技大學學報,2012,39(4):126-130.

[3] 鄧耀華,吳黎明,張力鍇,等.基于FPGA的雙DDS任意波形發生器設計與雜散噪聲抑制方法[J].儀器儀表學報,2009,30(11):2255-2261.

[4] 潘松,黃繼業.EDA 技術與VHDL(第2版)[M].北京:清華大學出版社,2007.

[5] 張萍.基于DDS 的寬帶信號發生器的設計[J].江南大學學報,2015,14(6):782-786.

[6] 閻石.數字電子技術基礎(第四版)[M].北京:高等教育出版社,2003.

[7] 王豐華,李建清,吳劍鋒.多源表面溫度信號發生裝置的硬件設計[J].儀表技術與傳感器,2014(1):83-85.

[8] 李雪梅,張宏財,王學偉.基于DDS技術的信號源設計[J].電測與儀表,2010,47(1):55-57.

[9] 楊萍,兀旦暉,楊良煜.DDS技術在正弦信號發生器中的應用[J].計算機測量與控制,2008,16(11):1738-1740.

[10] 李敏,金勵豪.矩形波信號發生電路的設計與分析[J].電子技術,2013(10):34-36.