0 引言

隨著人們對無線通信需求和質量的要求越來越高,無線通信設備的研發也變得越來越復雜,系統測試在整個設備研發過程中所占的比重也越來越大。為了更加方便地對所設計的系統進行調試和測試,無線信道模擬器是進行無線通信系統硬件測試不可或缺的儀器之一。目前,關于無線信道的模型研究比較多,而基于理論模型的硬件實現并不是很廣泛,同時成品十分昂貴,所以利用FPGA實現無線信道模擬器變得很有意義,節約了成本,而且也便于實現。FPGA是在PLD的基礎上發展起來的高性能可編程邏輯器件,使用FPGA進行數字邏輯設計,開發過程的投資較少,研制和開發的時間較短,并且因為引腳的可分配性電路一般比較簡單,修改和優化比較方便,并且在實際中易于使用。同時由于FPGA并行運算的特點,在大規模的數字運算中很有優勢,延時很小。

1 頻率選擇性衰落信道模型

多徑傳播信道的信道脈沖響應模式是模擬一個離散的廣義平穩非相關散射模型(WSSUS)。這樣的頻率選擇性衰落信道應該滿足兩個假設條件:

(1)在時間t(可能是幾個碼元長度)內,衰落的統計特性是平穩的;

(2)電波到達角和傳播時延是統計獨立變量。

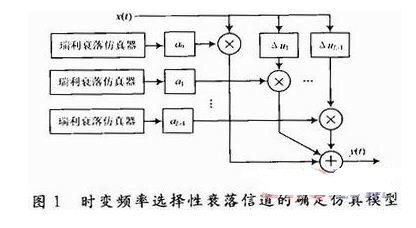

時變頻率選擇性衰落信道的確定仿真模型如圖1所示。

Jakes在參考文獻中介紹了一種單徑衰落信道的仿真,且在此基礎上提出了一種對頻率選擇性衰落信道的仿真方法。在原來第l徑中的多普勒相移bnl的基礎上,加上一個附加相移rnl,成為新的多普勒相移bnl+rnl,且保持其他參數不變。為了保證各個可分辨多徑之間相互獨立,所以必須選擇合適的bnl和rnl,其中比較簡單的一種方法是:

2 信道模擬器的FPGA設計

FPGA采用Xilinx公司的Virtex-2p,其中芯片工作時鐘為100MHz。本文設置N0=8,fm=200 Hz,

為了計算方便,將所得的值擴大32倍,也就是左移5位之后四舍五入成整數值,存入寄存器調用。所以信道模擬器的實現過程主要為各個正弦波的FPGA實現,與對應的系數相乘疊加成單徑衰落,輸入信號經過l個路徑時延之后疊加成為輸出信號。

2.1 正弦波的FPGA實現

FPGA產生正弦波一般可以采用直接產生和Xilinx或者Altera利用自帶DDS的IP核例化實現。FPGA直接產生是將三角函數值存入ROM中循環調用來產生正弦波,這樣占用的邏輯資源比較少,缺點就是過程很麻煩而且不夠靈活,模型需要8種頻率的正弦波和余弦波,而且fm也可能根據需要而變化,每一次變化就需要在ROM中重新賦初值,十分麻煩。因此本文選擇調用Xilinx自帶DDS的IP核,通過邏輯資源換取效率。DDS的模塊圖如圖2所示。

這樣,通過控制DATA的值得到所需頻率的正弦波。其中fclk為開發工作時鐘,DATA為輸入的頻率控制字,B為DATA的位寬,fout為所得的頻率。

2.2 時延模塊的FPGA實現

輸入通過時延后與各路徑的衰落系數相乘,然后各個路徑疊加成輸出信號。本文中時延采用計數分頻來實現,如延遲1μs,工作時鐘為100MHz,所以計算100個時鐘周期后,將輸入的值存入寄存器1,再計算100個時鐘周期后將輸入值存入寄存器2,依次類推,本為路徑l設置為5,所以最終有5個寄存器存放輸入值。

2.3 測試模塊的FPGA實現

最后需要將算得的數據上傳到Matlab進行統計分析,所以還需要FPGA串口驅動,以及Matlab打開驅動讀取FPGA算完的數據。根據異步串行通信的數據傳送格式,每一幀數據由起始位、數據位、奇偶校驗位和停止位組成,本文只選取了數據位,一共8位。通過串/并轉換接收數據,算完后存入RAM,然后調用數據,通過并/串轉換傳輸數據。

正弦波的輸出有10位,其中l位是符號位,另外9位是小數位,而系數左移5位后化成整數,在所得的整數中也有5位小數位,所以最終數據一共有19位,其中5位整數位,14位小數位。因為串口是8位一幀數據,為了運算簡便,選取了5位整數位,11位小數位,舍去最后3位小數,每個數分兩次傳輸。因為最后的數據分為實部和虛部,所以每個復數需要4幀數據傳輸。Matlab接收數據重新組合,還原成FPGA的計算結果。

3 模擬器的性能測試與分析

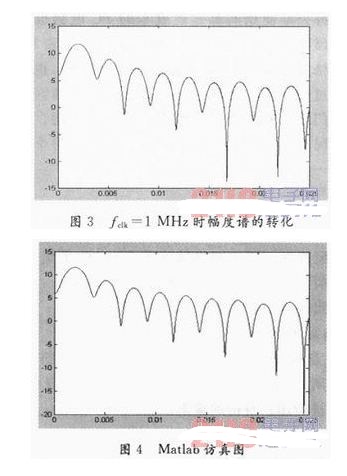

開發板的工作時鐘為100 MHz,DDS IP核延遲2個時鐘周期有輸出值,乘法器延遲1個時鐘周期有輸出值,所以系統總共有3個時鐘周期的延遲。串口傳輸數據比較慢,而且數據量太大容易出錯,所以將工作時鐘分別進行100倍分頻上傳衰落信道第一徑的25 000個數據進行觀察,工作時鐘變成1 MHz,將所得的幅度譜轉化成功率形式后如圖3所示,fclk=1 MHz的Matlab仿真如圖4所示。

圖3和圖4中橫軸單位均為s,縱軸單位均為dB。通過比較圖3和圖4發現實際產生的結果與仿真結果大致相同,也因為系數的取整和最后上傳數據的截斷有少許誤差,基本滿足要求。

4 結語

本文采用Jakes改進模型,基于FPGA模擬了無線信道的傳輸特性,最終經過驗證基本滿足要求。為了簡化實現過程,將系數取整以及傳輸數據進行截斷,產生一些誤差,在這方面可以采用浮點數表示系數得到更精確的值。