波形發生器廣泛應用于電子電路、自動控制和科學試驗領域,是一種為電子測量工作提供符合嚴格技術要求的電信號設備,和示波器、電壓表、頻率計等儀器一樣是最普通、最基本也是應用最為廣泛的電子儀器之一,幾乎所有電參量的測量都要用到波形發生器。隨著通信、雷達的不斷發展,對信號源的頻率穩定度、頻譜純度、頻率范圍和輸出頻率的個數以及信號波形的形狀也提出越來越多的要求。不僅要求能產生正弦波、方波等標準波形,還能根據需要產生任意波形,且操作方便,輸出波形質量好,輸出頻率范圍寬,輸出頻率穩定度、準確度及分辨率高,頻率轉換速度快且頻率轉換時輸出波形相位連續等。可見,研究制作高性能的任意波形發生器" title="任意波形發生器">任意波形發生器十分有必要,而且意義重大。

1 任意波形發生器的FPGA" title="FPGA">FPGA實現

系統框架如圖1所示,上位機產生任意波形數據,經USB2.0控制器CY7C68013A與FPGA(現場可編程門陣列)相連。將數據下載到FPGA的RAM當中,再通過硬件電路依次從波形存儲器中讀取出來,經D/A轉換及濾波后得到所需信號波形輸出。

![]()

關于DDS的基本原理與結構在這里就不再加以闡述,用FPGA按照DDS的基本原理和結構設計和實現一個任意波形發生器,所以DDS的幾個基本部分都是應當具備的。實現任意波形發生的關鍵在于把存放波形量化表的ROM換成了可以改寫的RAM,這樣通過與RAM的接口可以改變存放在波形RAM中的數據從而實現任意波形發生。這里主要介紹控制部分、相位累加器、波形RAM幾個模塊來敘述任意波形發生器的實現。

1.1 控制部分

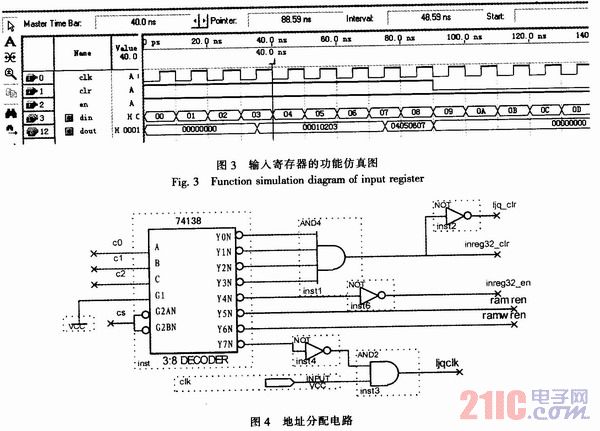

這個部分主要是要解決DDS模塊與單片機的接口問題。在FPGA的實現中,主要設計了2個模塊,一個是輸入寄存器模塊,為了接收單片機寫入的頻率控制字。另外一個是地址分配模塊,這樣單片機就可以通過不同的地址來選通FPGA各個模塊工作。設計中DDS采用了32位的相位累加器。這樣對于一個頻率控制字,單片機要分4次分別寫入4個字節;基于這樣的要求,設計了輸入寄存器模塊如圖2,這個部分主要是要解決DDS模塊與單片機的接口問題。

din[7..0]是該模塊與單片機數據線的接口,clr是低電平異步清零,en是高電平使能,elk為數據寫入時鐘,dout[31..O]是寄存器輸出的32位頻率控制字。該模塊工作過程為:當en為高電平,clr也為高電平時,elk的上升沿將輸入的8位數據鎖存進該模塊中,當鎖存完4個字節的數據后,自動將該4個字節的數據按照先寫入的在高位的順序組合成一個32 bit的數據輸出到dout[31..0]。

該模塊的功能仿真圖如圖3所示,看到當clr=‘1’并且en=‘1’時,經過4個時鐘,dout上將前4個時鐘的值‘00’、‘01’、‘02’、‘03’組成32位的‘00010203’數值輸出在dout上。

關鍵字:FPGA 任意波形發生器

地址分配模塊采用一個3/8譯碼器來實現地址選通的功能,如圖4所示。

由于累加器的清零是當“clr”=1的時候,所以在與門后加一個反相器,而頻率寄存器清零的條件是“clr”=0,所以,就可以直接與門后相連即可。3/8譯碼器的使能端接VCC,G2AN和G2BN連起來接CS,作為整個任意波形發生器模塊的片選信號,當低電平的時候選中,各模塊才開始工作。

地址鎖存模塊主要解決單片機P0口的分時復用問題。本設計選用的單片機為51系列單片機,其PO口既作為數據口,又作為地址總線的低8位,因此在使用時,需要將地址信號從分時復用的地址/數據總線中分離出來。本設計選用8D鎖存器7415373來作為地址鎖存器。當74LS373用作為地址鎖存器時,應使OEN為低電平導通輸出,此時,鎖存使能端G為高電平時,輸出Q1~Q8狀態與輸入D1~D8狀態相同;當G發生負跳變時,輸入端數據D1~D8鎖入Q1~Q8。因此在使用74LS373時,51單片機的ALE信號可以直接與74LS373的G相連。

1.2 相位累加器設計

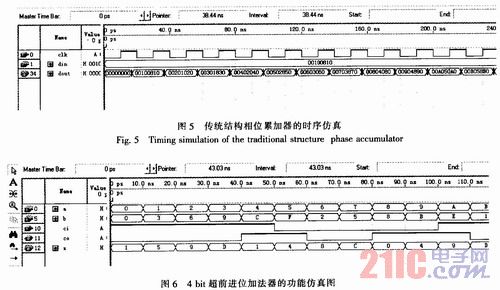

相位累加器用于對輸入頻率控制字進行累加運算,輸入頻率控制字決定輸出信號的頻率和頻率分辨率。因此相位累加器是整個DDS性能的關鍵部分。傳統的相位累加器是用1個加法器加1個D觸發器組成,調用其中的1個宏模塊設置成32位數據相加,再加另一個32位的宏模塊,就可以組成相位累加器。它在QuartusII軟件中的最高編譯頻率只有262.12 MHz,顯然不能滿足設計要求。其時序仿真如圖5所示。

通過仿真,當直接采用32 bit累加器的時候系統時鐘最大只能達到大約25 MHz,顯然是達不到要求的。從設計上看,它實質上是一個帶反饋的32位加法器,把輸出數據作為另一路輸入數據和從單片機傳來的頻率控制連續相加,產生有規律的32位相位地址碼。一般位數小的累加器可以通過FPGA中的進位鏈得到快速高效的電路,但是進位鏈必須位于臨近的LE(邏輯單元)或LAB(邏輯陣列塊)中,長的進位鏈會減少供其他邏輯使用的布線資源,同時過長的進位鏈也會制約系統頻率的提高,所以進位鏈不能太長。因此,在相位累加器的設計中,要解決的難題是設法提高工作速度。為了解決速度難題,需從兩個方面進行改進。

1.2.1 改進的流水線結構

在時序電路設計中為了提高速度,流水線結構是一種常用的設計方法。對于累加器來講,流水線結構就是把一個位數很長的加法拆分成N個位數較短的加法,在N個時鐘周期內做完然后輸出運算結果,N就是流水線的級數。采用流水結構以后由于加法器的字長變短了,對于FPGA來講加法器字長變短對工作頻率的提高是相當可觀的。當然,流水結構的使用并不能無限制地提高電路的工作速度。因此對于不同的器件來說,采用多少級流水對性能的提升比較大這個要經過仿真實驗才能得到一個比較肯定的值。

本文運用流水線結構對相位累加器進行設計,當m=8、n=4的情況下,相位累加器的工作頻率是最高的,達到了約70 MHz。但是為了進一步提高工作頻率,還需要結合下面的并行進位方法。

1.2.2 并行進位加法器

DDS累加器電路的設計采用了流水線結構,由8級4位加法器完成對32位控制字的累加。32位累加器的結果在送入相位幅度變化電路時,進行了高位截斷,只取高12位數據進行查表。因而,在8級的流水線結構中,前5級4位加法器實際上只貢獻了進位,在設計時,前4級加法器采用了超前進位鏈,而高位加法器不僅要給出進位值,還要獲得加法的結果,因此采用了QuartusII自帶的宏模塊結構。通過每一位的Pi、Gi和Ci-1值很容易求得該位進位值Ci。再與該位的和(Ai+Bi)相異或就得到最后的結果Si。即

![]()

采用上述結構,極大地提高了累加器的工作速度,其功能仿真圖如圖6所示,從圖中可以看出,此4 bit超前進位加法器完全滿足4位全加器的邏輯功能。

關鍵字:FPGA 任意波形發生器

下面就將前5級采用超前進位加法器的32位累加器和宏模塊中調用的4位全加器組成的32位相位累加器性能進行比較。

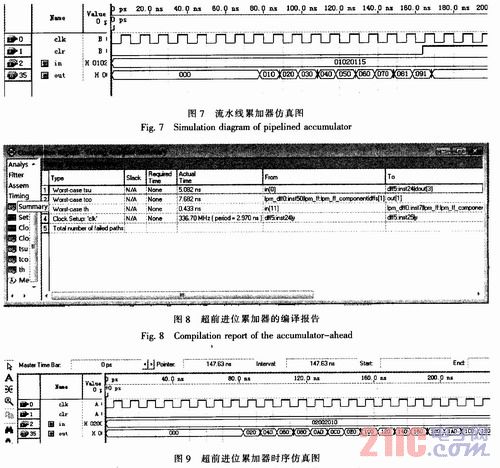

普通流水線累加器的模塊是由4位D觸發器,5位D觸發器和4位全加器作為基本元件,采用原理圖輸入的方法設計FPGA的流水線累加器。該模塊的設計參照流水線累加器結構進行,不同之處在于:由于相位累加器只用高位尋址,所以低位上為了和高位結果同時輸出而做延時作用的D觸發器件均被去掉了。這樣做的結果是,相位累加器輸出的低20位會因為提前輸出而混亂,但是由于高12位的輸出一定是正確的,這樣做既節省了資源,對結果又沒有任何影響。仿真結果證明假如不用流水線結構,32 bit相位累加器工作頻率最高達到約25 MHz。消耗的資源是82個LEs,而用了8級流水線結構后,編譯工作頻率最高達到了約317.79 MHz,資源消耗為186個LEs。可見在資源上的消耗換來了在性能上的極大提高。

流水線累加器的時序仿真如圖7所示:可以看出當輸入數據確定后,輸出結果要經過8個時鐘周期的延時后輸出,這是因為采用了8級流水結構。采用多少級流水結構,輸出就會延時多少個周期。同時也說明,對于輸入數據切換來說,該系統會有8個時鐘周期的延時,這是累加器采用流水線結構所不可避免的后果。事實上目前許多DDS專用芯片由于也采用流水線結構,所以本身也存在這樣的問題。由于8個時鐘周期的延時與系統時鐘相比,實際上還是很小的,在一般的應用場合下也是可以接受的。由于輸出的低20位未用,被省略了,只用了輸出的高12位,所以仿真波形中只有高12位的輸出結果。從輸出結果來看,高12位的輸出值是沒有錯誤的,與設計思想吻合。

下面介紹超進位流水線累加器的構成,比較流水線累加器內部結構圖和超前進位加法器的32位相位累加器的結構圖,可以看出兩個圖的區別,經過編譯以后的報告如圖8所示,可以看出經過改進后,編譯的最大工作頻率提高到了336.7 MHz。比單純的流水線累加器提高了將近20 MHz。

圖9是其時序仿真圖,從圖上可以看出,其值完全和功能仿真一致。

關鍵字:FPGA 任意波形發生器

1.3 雙口RAM設計

在設計波形存取電路時,首先應確定波形RAM的深度和字長。波形RAM的深度和字長與很多因素有關系。存儲器內部存儲的是一個或N個整周期的標準波形數據,存儲器容量越大,存儲的被采樣波形點數就越多,采樣效果就越好。存儲器的讀取速度是產生高頻波形的重要保證,讀取速度必須滿足相位累加器的累加速度,這樣才能保證直接數字合成過程的正常進行。同時,為了保證整個速度的同步性,選用一種同步RAM也是很必要的。

首先要確定波形RAM的深度和字長,由于任意波形發生器設計中選擇的DAC的字長是12位,很明顯波形RAM的字長也應該是12位;由于選擇的地址線位數為12位(即相位累加器輸出的高12位),尋址空間為4 K(4 096)個單元,即RAM存儲空間應為4 096x12 bit=49 152 bits,由于本設計所選擇的FPGA內部RAM最大可配置為119 808 bits,完全可以滿足49 152 bits的RAM空間設計。所以波形RAM設計為字長12位,地址線12位。針對任意波形發生器與普通DDS的不同,波形RAM的設計主要要求RAM具有讀寫兩個端口,這樣可以通過兩套地址系統,方便地進行RAM內容更新,即對RAM的寫操作;波形幅度量化數據的輸出,即對RAM的讀操作。結合ALTERA公司FPGA的特點,選擇了EP2C5F256C6這個芯片內部的雙口RAM來實現這個功能,如圖10所示。

芯片內部的雙口RAM具有讀地址和寫地址兩組地址線,數據線也分成了讀數據線和寫數據線兩組。這樣波形RAM的設計就非常簡單了,將寫數據線、寫地址線和單片機的數據線、地址線相連,用單片機更新RAM中的數據;將讀地址線和讀數據線分別與相位累加器的輸出和DAC的數據輸入相連,讀數據線上即輸出了波形幅度量化數據。

2 結束語

本文詳細闡述了產生任意波形數據和基于FPGA的硬件設計部分,以QuartusⅡ8.O軟件平臺作為開發工具,選用CycloneII" title="CycloneII">CycloneII系列的EP2C5-F256C6 FPGA芯片實現DDS結構中的數字部分,其中相位累加器是DDS的核心部件,重點闡述了相位累加器部分的設計,采用8級流水線結構借助前5級的超前進位模塊,編譯的最高工作頻率,由317.97 MHz提高到336.7 MHz,采用此種設計方法,節約了成本,縮短了開發周期,具有可行性。