摘 要: 在對10G" title="10G">10G城域網技術研究的基礎上,提出了10G網絡處理器" title="網絡處理器">網絡處理器的驅動程序設計中的一些思路并對此展開一定的分析和研究。

關鍵詞: 10G以太網 網絡處理器 驅動 應用程序接口 中斷服務程序

網絡技術的高速發展使下一代網絡技術不斷迎接新的挑戰。網絡處理核心從傳統的基于GPP(General Purpose Processor)的設計到基于ASIC(Application Specific Integrated Circuit)的設計再到基于網絡處理器NP(Network Processor)的設計,不斷向著高性能和高靈活性的方向發展。隨著城域網技術的發展,近年來許多廠家推出了10G的以太網設備。10G網絡處理器是實現10G以太網交換技術的關鍵點,10G網絡處理器的開發成為目前城域網建設中的一個重要環節。

本文介紹了10G的網絡處理器及其驅動程序,并對驅動程序的開發方法進行了研究和探討。

1 網絡處理器和驅動程序

網絡處理器是一種可編程器件,它特定地應用于通信領域的多種任務,例如數據包處理、協議分析、路由查找、數據的匯聚、防火墻、QoS等。網絡處理器具有多協議支持、優化的體系結構、專用的硬件設計和高速的數據轉發處理、高性能、高可靠性、豐富的流分類、擁塞管理、隊列調度、靈活的軟件開發和升級、靈活擴展和組合等特點。

網絡處理器器件內部由若干個微碼處理器和若干硬件協議處理器組成,多個微碼處理器在網絡處理器內部并行處理,通過預先編制的微碼來控制處理數據包的操作。而對于一些復雜的標準操作(如內存操作、路由表" title="路由表">路由表查找算法、QoS的擁塞控制算法、流量調度算法等)則采用硬件協議處理器進一步提高處理性能,從而實現業務的高靈活性與高性能的有機結合。

目前的網絡處理器系列有:面向網絡接入終端的設備;支持企業、電信市場接入和邊緣應用的設備(支持2.5Gbps數據傳輸率);支持網絡核心應用的設備(支持10Gbps數據傳輸率)等。

網絡處理器的驅動程序在系統中位于底層BSP(Board Support Packet)和上層軟件之間,如圖1所示。驅動程序是建立起上下層軟件之間通信的一個橋梁,為上下層軟件提供相應的接口,能夠把上層的命令解釋為底層軟硬件可以識別的代碼寫入芯片的寄存器中,包括兩個功能模塊:底層驅動模塊" title="驅動模塊">驅動模塊和業務驅動模塊。底層驅動模塊提供NP芯片初始化、配置、裝載微碼、建立維護NP查找結構、中斷處理、NP內部表項維護、 NP實時檢測等功能;業務驅動模塊為上層應用提供數據包發送和接收、路由表操作、ARP表操作、VLAN操作、端口表操作、MAC表操作等功能。

2 驅動程序開發方法研究

網絡處理器的芯片廠家需要提供相應的驅動開發軟件包,開發包中主要包括封裝了特定代碼的庫文件和說明文檔,這些庫文件在系統編譯時進行鏈接。開發人員通過調用驅動開發包中的API(Application Programming Interface)來完成對芯片的一系列操作。

2.1 芯片的初始化

包括正確地初始化網絡處理器芯片,使芯片能正常工作。網絡處理器芯片作為PCI設備掛在CPU的PCI總線上,它通過PCI總線識別,系統為其分配相應的PCI地址和中斷號。CPU通過網絡處理器的PCI地址對NP內部的寄存器進行訪問。

NP初始化步驟:

(1)調用識別函數識別NP:如果與廠商號相符,則說明NP已經被識別。

(2)配置NP的PCI設備:為 NP分配內存地址;為 NP配置中斷號。

(3)注冊PCI中斷處理程序" title="中斷處理程序">中斷處理程序:安裝芯片的中斷處理程序;將NP的PCI中斷處理程序與中斷號關聯。通常該中斷處理程序內部會調用一個全局的函數指針,開發者可以對其賦值,使能NP的PCI中斷。

(4)中斷事件處理方式:通常網絡處理器或交換芯片都定義有多種中斷事件,這些中斷事件由中斷事件狀態寄存器和中斷屏蔽寄存器進行控制。NP會定義若干種中斷事件,每種中斷用一個二進制位表示,該二進制位的取值決定中斷事件的中斷狀態(如:1表示有中斷,0表示無中斷)。中斷屏蔽寄存器則決定是否對中斷進行處理。

(5)NP的中斷事件類型:

數據幀中斷:當NP需要向CPU發數據包時,就產生此中斷,以通知主控系統有相關的數據幀和該數據幀的指針需要處理;

查找中斷:當NP的硬件表進行更新時,會產生此中斷。例如,NP的MAC地址學習機制和地址老化機制更新MAC表后,會將更新結果通過消息的形式上報給主控系統;

統計中斷:當NP的統計隊列有消息時,產生此中斷,通知主控系統某個統計計數器已經到達閾值。

(6)中斷處理流程如圖2所示。當主機接收到一個NP發生的PCI中斷時,NP的PCI ISR被觸發,PCI ISR確定哪一個NP發生中斷,將該NP編號通過消息的方式傳給驅動任務,驅動任務從中斷消息中獲得NP的ID號、中斷屏蔽寄存器的值和中斷事件寄存器的值,對中斷屏蔽寄存器和中斷事件寄存器的值進行位操作,對操作結果進行判斷,進而確定是否調用該中斷事件的中斷處理程序。

(7)初始化芯片上的數據通道:復位芯片上的寄存器并賦給默認值;指定硬件搜索引擎個數;設定統計計數器的門限值;設置外部存儲器值;啟動通道進入接收中斷狀態。

(8)加載硬件表結構和微碼:硬件表結構包括二層表、三層表、路由表、三層接口表、VLAN表等;表結構在微碼中定義;微碼中定義了數據包收發的方式和相應的操作方法。

?

2.2 數據包處理

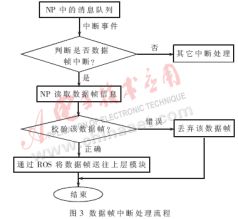

在中斷處理的基礎上進行數據包的接收,如圖3所示。CPU通過中斷方式接收來自網絡處理器的數據包。

(1)CPU接收來自網絡處理器數據包中斷后,會在驅動任務中調用響應的數據包的ISR,在該ISR中將數據包發給上層協議。

(2)按協議標準對數據包格式或內容進行修改和轉換。

(3)通過驅動API提供的函數發送數據包。

2.3 硬件表操作

硬件表是NP中由微碼定義的表查找結構,由NP完成MAC地址查找、VALN表添加、路由表搜索等各種表條目的添加和刪除等操作。

(1)由微碼定義和創建硬件表的種類、長度、編號等信息。

(2)由驅動在芯片初始化過程中加載硬件表結構并啟動微碼。

(3)驅動程序中要為上層協議提供硬件表添加、刪除、修改、顯示等接口。

隨著10G以太網技術的發展,已經有越來越多的廠家推出了自己的NP產品。高速網絡處理器已經成為當前以太網研究中的一個重點,同時需要對芯片的驅動程序深入開發。本文對10G網絡處理器的驅動程序設計進行了分析和研究,提出了驅動軟件開發中的一些思路。由于目前與10G以太網技術相關標準和技術的成熟和完善還需要一定的時間;各廠家使用不同的軟硬件開發環境;存在不同的嵌入式操作系統;以及一些廠家使用專用的代碼開發和調試工具等因素,使NP及其驅動程序的發展還需要進一步地提高。今后的主要工作包括:提高不同廠家的設備之間互通性和兼容性;加強NP軟件代碼的規范性和可移植性;完善NP驅動軟件的開發方法。

10G網絡處理器作為下一代網絡的關鍵,以其多方面的優勢,可以較好地滿足未來高速網絡技術發展的需求,具有非常廣泛的發展空間。

參考文獻

1 IEEE 802.3ae-2002. IEEE Standard for Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications-Media Access Control (MAC) Parameters. Physical Layer and Management Parameters for 10 Gb/s Operation

2 IEEE 802.3-2002 Edition. IEEE Standard for Information technology--Telecommunications and information exchange between systems--Local and metropolitan area networks--Specific requirements--Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications

3 IEEE 802.3-2002 Edition. IEEE Standard for Information technology--Telecommunications and information exchange between systems--Local and metropolitan area networks--Specific requirements--Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications. By EZchip Technologies Ltd., 2003.

4 陳一帥,趙永祥.網絡處理器及應用.網絡世界, 2000;7