摘 要:在對G.726語音編解碼標準分析的基礎(chǔ)上給出了基于FPGA的DSP設(shè)計流程,利用MATLAB/Simulink、DSP Builder和SOPC Builder工具設(shè)計了G.726語音編解碼器" title="編解碼器">編解碼器,通過仿真實驗驗證了所設(shè)計的編解碼器模型的正確性,實現(xiàn)了編解碼器在SoPC系統(tǒng)中的綜合。

關(guān)鍵詞:ADPCM MATLAB/Simulink DSP Builder FPGA SoPC

G.726是ITU前身CCITT于1990年在G.721和G.723標準的基礎(chǔ)上提出的關(guān)于把64kbps非線性PCM信號轉(zhuǎn)換為40kbps、32kbps、24kbps、16kbps的ADPCM信號的標準。G.726標準算法簡單,語音質(zhì)量高,多次轉(zhuǎn)換后語音質(zhì)量有保證,能夠在低比特率上達到網(wǎng)絡(luò)等級的話音質(zhì)量,從而在語音存儲和語音傳輸領(lǐng)域得到廣泛應(yīng)用[2]。

G.726語音壓縮算法已經(jīng)能夠在以DSP處理器為核心器件的DSP應(yīng)用系統(tǒng)上實現(xiàn)。但開發(fā)以DSP處理器為核心的DSP應(yīng)用系統(tǒng)所采用的開發(fā)方法是自底向上的設(shè)計流程,嚴重影響開發(fā)的效率和成功率。面對現(xiàn)代通信技術(shù)的發(fā)展,DSP處理器已暴露出硬件結(jié)構(gòu)的不可變性、處理速度比較慢等不足[1]。現(xiàn)代大容量、高速度的FPGA及其相關(guān)的開發(fā)技術(shù),在可重配置的DSP應(yīng)用領(lǐng)域、DSP數(shù)據(jù)大吞吐量和數(shù)據(jù)的純硬件處理方面,有獨特的優(yōu)勢[1]。新的基于FPGA的DSP系統(tǒng)級開發(fā)工具以及完整的軟件開發(fā)平臺,使得設(shè)計者能采用自頂向下的開發(fā)方法進行FPGA的DSP設(shè)計,設(shè)計效率大為提高。

本文分析了G.726標準,給出了基于FPGA的DSP設(shè)計開發(fā)流程" title="開發(fā)流程">開發(fā)流程,利用MATLAB/Simulink、Altera公司的DSP Builder和SOPC Builder工具設(shè)計了語音記錄SoPC系統(tǒng)中的G.726語音編解碼器" title="語音編解碼器">語音編解碼器,并實現(xiàn)了編解碼器在該系統(tǒng)中的綜合。采用基于FPGA的G.726語音編解碼器的語音記錄嵌入式系統(tǒng)具有運行速度快、體積小巧、開發(fā)周期短等優(yōu)點。

1 G.726語音編解碼標準

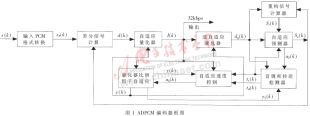

G.726編碼器框圖如圖1所示。G.726語音編碼器首先將輸入的A律或μ律的log-PCM信號S(k)轉(zhuǎn)換成線性的PCM碼Sl(k),然后與預(yù)測信號Se(k)相減產(chǎn)生差分信號d(k),再對差值信號進行自適應(yīng)量化" title="自適應(yīng)量化">自適應(yīng)量化,產(chǎn)生2~5比特ADPCM碼I(k)。一方面將I(k)送至解碼器;另一方面逆自適應(yīng)量化器利用I(k)產(chǎn)生量化差分信號dq(k)。預(yù)測信號Se(k)和量化差分信號dq(k)相加產(chǎn)生本地重構(gòu)信號Sr(k)。自適應(yīng)預(yù)測器是由二階極點和六階零點組成的濾波器,根據(jù)重構(gòu)信號Sr(k)和量化差分信號dq(k)產(chǎn)生輸入信號的預(yù)測信號Se(k)。量化器比例因子" title="比例因子">比例因子自適應(yīng)單元根據(jù)輸入信號的特性計算量化器比例因子y(k),用來控制量化器和逆量化器,以獲得自適應(yīng)功能。量化器比例因子由快速因子和慢速因子兩部分,以及速度控制因子al(k)對這兩部分的加權(quán)組成。速度比例因子al(k)的計算由自適應(yīng)速度控制單元與音調(diào)和傳送檢測器單元完成。

G.726語音解碼器的解碼過程實際上已經(jīng)包含在編碼器中,只是多了輸出PCM格式轉(zhuǎn)換單元和同步串行編碼調(diào)整單元。輸出PCM格式轉(zhuǎn)換是將線性PCM碼轉(zhuǎn)換為A律或μ律PCM碼;同步串行編碼調(diào)整是為了防止多級傳輸、轉(zhuǎn)換過程中的誤差。

2 基于FPGA的DSP設(shè)計開發(fā)流程

利用傳統(tǒng)的開發(fā)工具,基于FPGA的DSP開發(fā)者在算法確定后只能直接使用VHDL或VerilogHDL語言進行FPGA的DSP系統(tǒng)設(shè)計,開發(fā)需要較長的周期,且難度比較大。目前出現(xiàn)的基于FPGA的DSP開發(fā)工具,如DSP Builder、SOPC Builder、System Generator等,使得設(shè)計者能遵循一條類似于軟件設(shè)計流程的開發(fā)方法進行FPGA的DSP設(shè)計,設(shè)計效率大為提高。

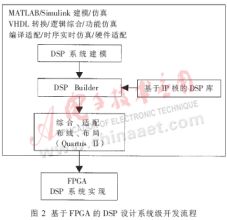

本文給出利用MATLAB/Simulink和Altear公司的開發(fā)工具進行基于FPGA的DSP設(shè)計的開發(fā)流程。DSP Builder是Altera公司推出的面向DSP開發(fā)的系統(tǒng)級工具。它作為MATLAB的一個Simulink工具箱(ToolBox)出現(xiàn)。MathWorks的MATLAB和Simulink系統(tǒng)級的設(shè)計工具具備了算法開發(fā)、仿真、驗證能力,DSP Builder將這些工具與Altera的開發(fā)工具組合在一起,為用戶提供了一個完整的DSP開發(fā)平臺。

基于FPGA的DSP設(shè)計系統(tǒng)級開發(fā)流程如圖2所示。其步驟:(1)在MATLAB/Simulink中對DSP系統(tǒng)進行建模,用圖形方式調(diào)用Altera DSP Builder和其他Simulink庫中的圖形模塊(Block),構(gòu)成系統(tǒng)級和算法級設(shè)計框圖,同時利用Simulink完成模型仿真。(2)利用DSP Builder將Simulink的模型文件(.mdl)轉(zhuǎn)化成通用的硬件描述語言VHDL文件(.vhd),轉(zhuǎn)換獲得的HDL文件是基于RTL級的VHDL描述。(3)對轉(zhuǎn)換過程中產(chǎn)生的VHDL的RTL代碼和仿真文件進行綜合、編譯適配以及仿真。所用工具可以是Altera的Quartus II軟件,也可以是第三方軟件工具。(4)在DSP Builder中直接下載到FPGA用戶開發(fā)板上,也可通過Quartus II完成硬件的下載、測試。整個開發(fā)流程幾乎可以在同一環(huán)境中完成,真正實現(xiàn)了自頂向下的設(shè)計流程,極大地縮短了DSP設(shè)計周期。

3 G.726語音編解碼器在SoPC中的實現(xiàn)

3.1 G.726標準算法的簡化

本文設(shè)計的編解碼器是在語音記錄系統(tǒng)中實現(xiàn)G.726建議的速率為32kbps的ADPCM算法,根據(jù)實際情況對算法進行了一些簡化和改進。

具體簡化如下:(1)由于此系統(tǒng)中編解碼器的輸入信號是線性PCM碼,因此PCM碼轉(zhuǎn)換模塊可以省略。(2)這個算法是用在單純的語音存儲中,可不進行單音/過渡音檢測。(3)對量化器比例因子y(k)的更新進行簡化。y(k)的更新計算為:

y(k)=al(k)yu(k-1)+[1-al(k)]yl(k-1)????????????? (1)

一般情況下,只有語音信號時,al(k)是趨于1的;當輸入為平穩(wěn)信號時,al(k)的值則在0至1之間。對語音存儲系統(tǒng),在輸入只有語音的情況下可以粗略地認為al(k)的值近似為1,從而將計算得到的快速比例因子yu(k)直接作為新的比例因子y(k),即y(k)=yu(k-1),降低了算法的復(fù)雜度。

3.2 G.726算法在Simulink中的建模

在Simulink中利用Altera DSP Builder庫模塊建立用于FPGA定點實現(xiàn)的模型。這里給出G.726編碼器模型的設(shè)計。整個設(shè)計采用多層次結(jié)構(gòu),在頂層設(shè)計模型下包括多個子系統(tǒng)模塊模型,如自適應(yīng)量化器子系統(tǒng)模型、逆自適應(yīng)量化器子系統(tǒng)模型、量化器比例因子自適應(yīng)子系統(tǒng)模型等。下面重點分析編碼器系統(tǒng)中的頂層設(shè)計模型及自適應(yīng)量化器子系統(tǒng)模型。

3.2.1 編碼器的頂層設(shè)計模型

頂層模型提供了對外的PCM語音接口,同時也提供了對Avalon總線的接口,使得所設(shè)計的編碼器模塊可通過SOPC Builder集成為Nios II系統(tǒng)的一個外圍設(shè)備。模型中的自適應(yīng)量化器模塊、逆自適應(yīng)量化器模塊、量化器比例因子自適應(yīng)模塊和自適應(yīng)預(yù)測器模塊均為HDL SubSystem。編碼器的頂層設(shè)計模型如圖3所示。

?

其中SignalCompiler模塊是DSP Builder的心臟。其主要完成的功能包括:(1)將Simulink設(shè)計轉(zhuǎn)變成可綜合的RTL級VHDL代碼;(2)產(chǎn)生VHDL testbenches;(3)為LeonardoSpectrum、Synplify和Modelsim第三方EDA工具產(chǎn)生Tcl腳本文件;(4)為Quartus II的仿真產(chǎn)生仿真矢量文件(.vec);(5)產(chǎn)生PTF配置文件,用于將設(shè)計自動地輸給SOPC Builder工具。SignalCompiler控制著設(shè)計系統(tǒng)的綜合、編譯和仿真的流程。

根據(jù)G.726語音算法的需求,系統(tǒng)需要兩個時鐘,分別為8kHz和120kHz,其中120kHz用于自適應(yīng)預(yù)測器子系統(tǒng)。因此需要在模型中利用鎖相環(huán)模塊PLL實現(xiàn)多時鐘設(shè)計,產(chǎn)生所需的兩個時鐘,DSP Builder根據(jù)PLL輸出時鐘的上升沿工作。在Simulink設(shè)計圖上不會顯示時序模塊的時鐘引腳,而是當SignalCompiler將系統(tǒng)轉(zhuǎn)化為VHDL文件時才自動地把時序模塊的時鐘引腳與相應(yīng)時鐘相連。

3.2.2 編碼器的自適應(yīng)量化器子系統(tǒng)模型

自適應(yīng)量化器模型如圖4所示。自適應(yīng)量化在對數(shù)域內(nèi)進行,在用量化比例因子對差分信號進行規(guī)格化處理后,通過查找量化器規(guī)格化輸入/輸出特性表,即得到ADPCM碼。對數(shù)運算在Simulink中的實現(xiàn)是借助于查找表的方式,使用DSP Builder子庫中的LUT模塊;規(guī)格化輸入/輸出特性表的實現(xiàn)是采用ROM查表法的方式,用ROM EAB模塊實現(xiàn)。

由于ADPCM語音編解碼算法最終要在FPGA上實現(xiàn),Simulink的浮點值必須轉(zhuǎn)換成定點值并能在目標硬件實現(xiàn)。硬件中表示定點值的位數(shù)以及小數(shù)點的位置不但會影響構(gòu)成硬件系統(tǒng)的資源利用率,還影響系統(tǒng)的特性。本設(shè)計中根據(jù)信號的應(yīng)用范圍判定小數(shù)點的位置,并根據(jù)實際需要改變小數(shù)點右側(cè)的位數(shù),以節(jié)省硬件資源,靈活地應(yīng)用總線控制庫中的模塊來對總線進行截位、增位、位提取或進行數(shù)據(jù)類型轉(zhuǎn)換等操作,以達到所需求的精度。

3.3 G.726算法模型的仿真過程

利用MATLAB/Simulink和DSP Builder工具進行基于FPGA的DSP設(shè)計需要進行一系列的仿真。在Simulink中設(shè)計的模型首先要在Simulink中仿真,不僅是驗證模型的正確性,而且因為用于ModelSim仿真的TestBench文件中的輸入信號激勵是由SignalCompiler根據(jù)Simulink的仿真結(jié)果產(chǎn)生,并且只有仿真后利用SignalCompiler轉(zhuǎn)換產(chǎn)生的VEC文件才有效。在Simulink中完成仿真驗證后,使用SignalCompiler將模型進行設(shè)計轉(zhuǎn)換。

對于設(shè)計轉(zhuǎn)換后產(chǎn)生的VHDL文件,必須進行RTL級仿真。因為Simulink中模型仿真是算法級的,而生成的VHDL描述是RTL級的,兩者描述的情況可能不完全符合,因此需要對生成的RTL級VHDL代碼進行功能仿真。仿真可通過在ModelSim中運行轉(zhuǎn)換過程所生成的Tcl腳本文件。最后可以利用轉(zhuǎn)換過程生成的VEC文件,在Quartus II軟件中進行時序仿真。

本設(shè)計對上述建模的語音編碼器完成了仿真,Simulink的仿真結(jié)果與ModelSim的仿真結(jié)果基本一致,表明兩者描述相符合;Quartus II的時序仿真結(jié)果表明所設(shè)計的語音編碼器達到了預(yù)期的結(jié)果。

?

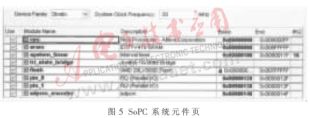

3.4 編解碼器模塊在SoPC系統(tǒng)中的綜合

編碼器模型在Quartus II綜合和編譯后,可以使用SOPC Builder將其作為外圍設(shè)備添加到Nios II系統(tǒng)中。SignalCompiler生成的PTF配置文件可用于將設(shè)計自動地輸給SOPC Builder工具。所設(shè)計的編碼器出現(xiàn)在SOPC Builder的模塊池中,將其添加到所創(chuàng)建的系統(tǒng)中即可。所建SoPC系統(tǒng)元件頁如圖5所示,圖5中只列出了語音記錄系統(tǒng)的一部分組件。利用SOPC Builder即可生成一個完整的系統(tǒng),最后生成編程文件,進行硬件的下載,完成G.726語音編碼器在SoPC中的設(shè)計。

由于DSP Builder中的DSP基本模塊以算法級的描述出現(xiàn),而且采用Simulink圖形化界面,因此設(shè)計非常直觀,實現(xiàn)了自頂向下的開發(fā)流程。與傳統(tǒng)DSP開發(fā)相比,大大縮短了創(chuàng)建DSP設(shè)計的硬件的開發(fā)周期。設(shè)計的編解碼器可作為Nios II系統(tǒng)的外圍設(shè)備,通過SOPC Builder很方便地綜合到SoPC系統(tǒng)中。同時,由于設(shè)計是在基于FPGA的SoPC上實現(xiàn),因此可以根據(jù)實際需求更改設(shè)計,對系統(tǒng)進行重配置,具有很高的靈活性。本G.726語音編解碼器的性能基本上達到了設(shè)計要求。

參考文獻

1 潘 松,黃繼業(yè),王國棟.現(xiàn)代DSP技術(shù)[M].西安:西安電子科技大學(xué)出版社,2003

2 王海平,劉 琚.定點DSP實現(xiàn)ITU-T G.726語音編解碼標準[J].電子技術(shù),2003;(12):33~35

3 任愛鋒,初秀琴.基于FPGA的嵌入式系統(tǒng)設(shè)計[M].西安:西安電子科技大學(xué)出版社,2004

4 Shorten DSP Design Cycle Using Complex IP in MATLAB/Simulink to Quartus II Flow[J].Altera Corporation News & Views,Third Quarter 2002

5 Altera Corporation. DSP Builder User Guide,2004

6 Altera Corporation. DSP Builder Reference Manual,2004