1 前言

在任何一個(gè)高速高分辨率的模數(shù)轉(zhuǎn)換器中,高精度和快速比較器總是起著至關(guān)重要的作用。與其它種類的ADC 相比,流水線ADC 有著高速、高分辨率的特點(diǎn)。因此,它在電子系統(tǒng)中,有著廣泛的應(yīng)用。流水線ADC由許多子FLASHADC 構(gòu)成。流水線ADC 的特性中,特別是速度,功耗和失調(diào)電壓對(duì)整個(gè)電路有著很重要的影響。適合流水線的動(dòng)態(tài)比較器主要有三種:電阻分壓比較器、差分比較器和電容差分比較器[1]。但是他們可能消耗過多的功耗和較大的失調(diào)電壓。因此,前置運(yùn)放鎖存比較器的優(yōu)勢體現(xiàn)在3.5 位的子FLASHADC 或者更高分辨率的子FLASHADC 中。在考慮上面提及的因素后,本文給出了時(shí)間延遲、失調(diào)電壓和比較器的踢回噪聲的理論分析,并根據(jù)此分析,設(shè)計(jì)和優(yōu)化了比較器電路。

2 預(yù)放大鎖存比較器的工作原理

前置增益運(yùn)放鎖存比較器的原理是前置增益運(yùn)放放大輸入信號(hào),被放大后的信號(hào)輸入到鎖存比較器,最后信號(hào)通過一個(gè)普通的RS 觸發(fā)器,得到最終比較結(jié)果。這種結(jié)構(gòu)結(jié)合了前置增益運(yùn)放對(duì)輸入信號(hào)負(fù)指數(shù)響應(yīng)和鎖存比較器對(duì)輸入信號(hào)正指數(shù)響應(yīng)的優(yōu)點(diǎn)。因此前置增益運(yùn)放鎖存比較器與其它鎖存比較器相比,有較小的傳輸?shù)难舆t。鎖存比較器的失調(diào)電壓除以預(yù)放大器的增益后折算到運(yùn)放的輸入端。因此,前置增益運(yùn)放比較器的失調(diào)電壓主要來自于預(yù)放大器。通過前置增益運(yùn)放比較器輸入端的踢回噪聲,在信號(hào)的比較階段混淆了輸入信號(hào)。沒有隔離電路可能導(dǎo)致采樣電路的不穩(wěn)定性和不精確的比較結(jié)果。因此在鎖存比較器輸入端和前置增益運(yùn)放的輸出端在之間需要一個(gè)隔離電路[2]。

3 電路的結(jié)構(gòu)

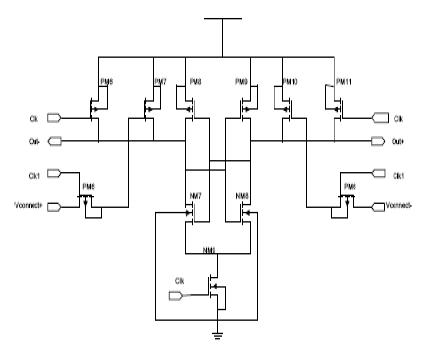

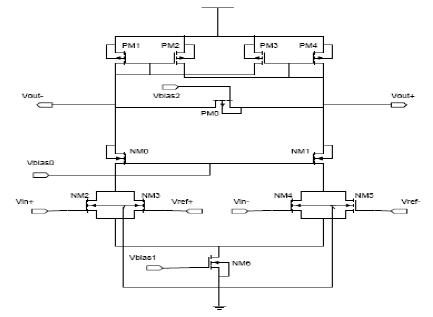

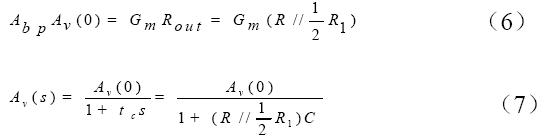

圖1 給出了前置增益運(yùn)放鎖存器的電路結(jié)構(gòu)。前置增益運(yùn)放有兩個(gè)差分對(duì),分別由NM2,NM3,NM4 和NM5 組成。PM1,PM2,PM3,PM4 交叉相連形成一個(gè)正反饋回路,并且增大了前置放大器的增益。NM9,NM10,NM11,PM6,PM11 是開關(guān)。電路的工作流程為:當(dāng)Clk 為低的時(shí)候,鎖存比較器被復(fù)位,與此同時(shí),Clk1 為高,鎖存比較器能夠接收到前置增益運(yùn)放的放大的信號(hào)。加載在NM2 和NM3 柵上的差分輸入信號(hào),分別NM4 與NM5 柵上正相基準(zhǔn)電平和負(fù)相基準(zhǔn)電平相比較。兩端各自產(chǎn)生的差分電流,流過共柵級(jí)后,差分負(fù)載迫使它流過接在輸出兩端的電阻R1,產(chǎn)生一個(gè)電壓差(Vout+—Vout-),送到鎖存比較器的輸入端。當(dāng)Clk 為高電平是,鎖存比較器開始工作,差值(Vout+—Vout-)被交錯(cuò)連接的正反饋回路放大,直至穩(wěn)定,一直到低電平的Clk 的到來。

(a) 前置增益運(yùn)放

(b) 鎖存比較器

圖1 前置增益鎖存比較器

3.1 前置增益運(yùn)放鎖存比較器的失調(diào)電壓

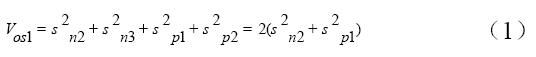

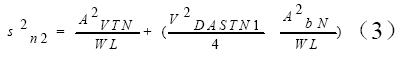

前置增益運(yùn)放鎖存比較器結(jié)構(gòu)由帶正反饋的前置增益運(yùn)放和鎖存比較器組成,所以比較器的失調(diào)電壓主要由前置增益運(yùn)放和鎖存比較器的失調(diào)電壓組成。前置運(yùn)放放大了的差分信號(hào)用來出發(fā)鎖存比較器,并且電路的正反饋提高了比較器的速度,增益也提高了。前置運(yùn)放的失調(diào)電壓Vos1 主要是由于NM2,NM3,NM4 和NM5 的不匹配造成的。根據(jù)文獻(xiàn)[3]的分析方法,可以得到這樣的式子[3][4],

公式(1)中,

,

,

而Vos2 主要由PM7,PM8,PM9,PM10 失配以及PM6 與PM12 關(guān)斷引入的失配引起的電荷Q 所組成的,表達(dá)式為,

因此,總體的失調(diào)電壓為,

根據(jù)公式(5),只要Av 足夠的大,那么整個(gè)比較器的運(yùn)放的失調(diào)就可以認(rèn)為主要由前置增益運(yùn)放的失調(diào)電壓Vos1 造成的。

在公式(1)~(5)中,Avtn, Avtp, n Ab , 和p Ab 是與工藝相關(guān)的常數(shù), 和

和 是前置運(yùn)放負(fù)載晶體管的失調(diào)電壓,

是前置運(yùn)放負(fù)載晶體管的失調(diào)電壓,![]() 和

和![]() 是輸入晶體管的失調(diào)電壓,因此加大晶體管的面積可以得到較小的失調(diào)電壓。但是,這種方法將加大版圖的面積以及寄生電容,而且也會(huì)降低比較器的速度。其實(shí)不用增大所有管子的面積,就可以減小比較器的失調(diào)電壓。根據(jù)公式(5),可以增大增益Av 來減小Vos2 對(duì)比較器的失調(diào)影響。根據(jù)公式(1),可采用減小Vos1的方法如下:1)增大Av,用來減小NM2 和NM3 的失配對(duì)Vos1 的影響;2)適量的增加NM2 和NM3 的面積,以減小閾值電壓的失配對(duì)Vos1 的影響。

是輸入晶體管的失調(diào)電壓,因此加大晶體管的面積可以得到較小的失調(diào)電壓。但是,這種方法將加大版圖的面積以及寄生電容,而且也會(huì)降低比較器的速度。其實(shí)不用增大所有管子的面積,就可以減小比較器的失調(diào)電壓。根據(jù)公式(5),可以增大增益Av 來減小Vos2 對(duì)比較器的失調(diào)影響。根據(jù)公式(1),可采用減小Vos1的方法如下:1)增大Av,用來減小NM2 和NM3 的失配對(duì)Vos1 的影響;2)適量的增加NM2 和NM3 的面積,以減小閾值電壓的失配對(duì)Vos1 的影響。

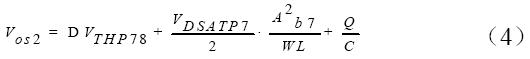

圖2 為比較器的版圖。版圖的左邊為前置運(yùn)放的版圖,右邊為鎖存比較器的版圖。為了減小由于版圖的失配帶來的比較器的輸入電壓,前置運(yùn)放和鎖存比較器分別采用對(duì)稱結(jié)構(gòu),增加比較器的對(duì)稱性。

圖2 比較器的版圖

3.2 踢回噪聲

在前置運(yùn)放的輸出端和鎖存比較器的輸入端之間需要一個(gè)隔離電路來減小踢回噪聲[2]。在鎖存比較器的兩個(gè)輸入端的晶體管的前面,分別加上一個(gè)PMOS管(PM6,PM11)作為開關(guān)管,晶體管的共柵電壓用來控制信號(hào)。因此,踢回噪聲對(duì)整個(gè)前置增益運(yùn)放鎖存比較器的影響就顯著的減小了。

3.3 傳輸延遲時(shí)間的改善

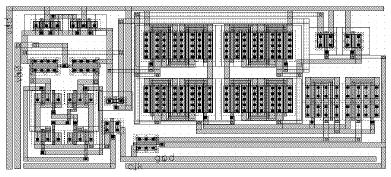

有兩種方法減小傳輸比較器的延遲:1)降低前置增益運(yùn)放的時(shí)間常數(shù);2)加大前置增益運(yùn)放的A(s)[5][6]。

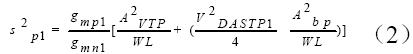

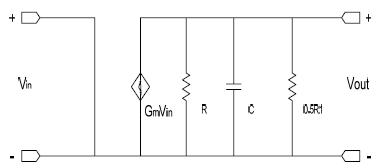

圖3 為前置增益運(yùn)放的交流小信號(hào)等效模型。根據(jù)圖3,可得到等式(6),(7)

圖3 前置增益運(yùn)放的小信號(hào)等效模型

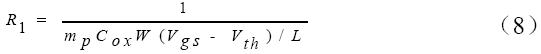

在上面的式子中,Av(0)為前置增益運(yùn)放的直流小信號(hào)增益,Rout 是運(yùn)放的等效輸出阻抗, c t 為時(shí)間常數(shù)。R1 可以通過工作在深線性區(qū)的PMOS 管來代替,表達(dá)式為,

根據(jù)公式(6)(7),減小R1 可以使得 c t 減少,從而使響應(yīng)速度指數(shù)增加,但是,同時(shí)減小R1,也使得Av(0)變小,從而使得響應(yīng)速度線性下降。由此可見,與Av(0)相比, c t 對(duì)延遲時(shí)間的影響要顯著多。因此,在設(shè)計(jì)時(shí),對(duì)Av(0)要有個(gè)合理的設(shè)置。

4 模擬仿真與結(jié)果分析

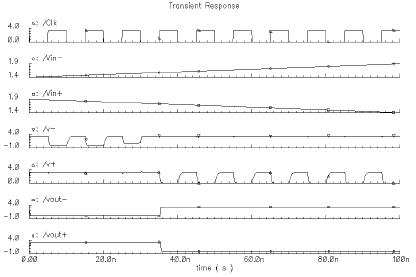

在Cadence Composer 環(huán)境,使用Spectre 對(duì)本文的比較器進(jìn)行仿真。時(shí)鐘的模擬頻率為100MHz,電源電壓為3.3v,模擬的條件為Typical。

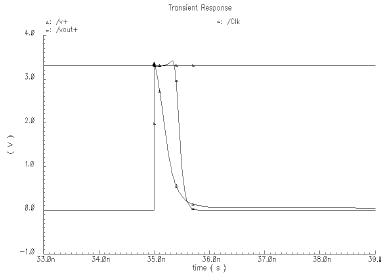

在圖4 中,Vin+和Vin-為差分三角波信號(hào),頻率為2.5MHz,峰-峰值為1.455v~1.855v。Vref+和Vref-為差分直流信號(hào),它們的差值為31.25mv,4 位子FlashADC 的1/2LSB。信號(hào)的共模電壓為1.65v。V+和V-分別為鎖存比較器的正負(fù)端輸出,Vout+和Vout-分別為最終輸出的正端和負(fù)端。從圖4可以看出當(dāng)Vin+和Vin-的差值小于1/2LSB 時(shí),Vout+和Vout-的電壓值發(fā)生翻轉(zhuǎn)。圖5為圖4的局部放大圖,可以看出傳輸比較器的延遲為680ps。在這種情況下整個(gè)電路消耗0.29mw 的功耗。

圖4 比較器的仿真波形

圖5 圖4的局部放大圖

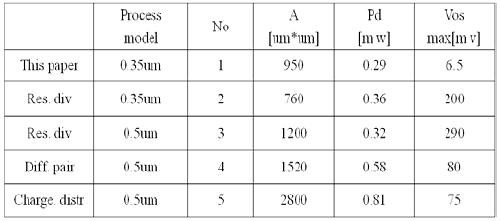

表1 中,前置增益動(dòng)態(tài)比較器,電阻分配比較器(0.35um 和0.5um)、差分對(duì)比較器和電荷分配型比較器的性能進(jìn)行總結(jié)。從表1中,可以看出與其它比較器相比,前置增益運(yùn)放動(dòng)態(tài)比較器擁有最低的功耗和失調(diào)電壓。

表1 五種比較器的性能[1]

5 結(jié)論

本文介紹了一種高速電壓比較器,采用了前置增益運(yùn)放鎖存比較器。根據(jù)仿真結(jié)果,比較器在100MHz 的采樣頻率下消耗0.29mw 的功耗,并且具有6.5mv的低失調(diào)電壓。因此,此比較器較適合用于流水線ADC。

本文作者的創(chuàng)新點(diǎn):采用前置增益運(yùn)放鎖存的結(jié)構(gòu)并結(jié)合版圖,減小了失調(diào)電壓;增加了隔離電路,減小了踢回噪聲;分析了前置增益運(yùn)放,改善了傳輸延遲時(shí)間。

參考文獻(xiàn):

[1] Sumanen L, WaltariM, Hakkarainen V. CMOS dynamic comparators for pipeline A/D converters[A].IEEE Int Circ and Syst Symp[C].2002.Vol.5:157-160.

[2] Figueiredo P M,Vital J C.Low kickback noise techniques for CMOS latched comparators[A].IEEE Int Circ and Syst Symp[C].Vancouver Canada.2004.I-537-540.

[3] Gray P R,Hurst P J.Analysis and design of analog integrated circuits FM].New York:John Wiley& Sons,Inc.2001.

[4] Pelgrom MJM,Duinmaijer ACJ,Welbers APG,et al.Matching properties of MOS transistors.IEEE J Solid-State Circuits,1989,24(5):1433

[5] KY Kim, N. Kusayanagi, and A Abidi, A 10-b 100-MS/s CMOS A/D Converter, IEEE Journal of Solid-State Circuits, 32(3), 1998, 302-311.

[6] 劉濤,楊文榮,冉峰,王坤,鄧霜。一種高速高分辨率C M O S比較器[z],微計(jì)算機(jī)信息,2006,04:209-211