在使用 MCU 的嵌入式系統設計中,當程序或者數據內存占用太大而無法放入片上閃存或 SRAM 時,開發者通常考慮使用 SDRAM。

別問我為什么你的 MCU 不支持 SDRAM。

SDRAM 是同步動態隨機存取存儲器的縮寫。在微控制器應用中,微控制器通過使用外部存儲控制器(EMC)操作訪問 SDRAM ,SDRAM 時鐘頻率通常為 100MHz 或 133MHz。

外部存儲控制器通常不支持 DDR SDRAM, 數據只是單邊沿采樣,即并行數據總線可以接受一個命令并在每個時鐘周期傳輸一個數據字。

在 SDRAM 中執行程序是使用 SDRAM 的一種典型用法, 小編這里就介紹一下 SDRAM 中執行程序的方法和 SDRAM 執行程序的性能基準。

SDRAM 初始化

SDRAM 必須在使用前進行配置,SDRAM 初始化分為 6 個步驟。

配置 EMC 寄存器的 SDRAM 時鐘頻率、字節順序和時序參數。

SDRAM 的時序比較復雜,用戶需要通過查閱相關 SDRAM 芯片的手冊獲得時序參數(如刷新周期、預充電命令周期、自刷新退出時間、寫恢復時間等等)。

發送 NOP 命令

發送預充電命令

發送兩次自動刷新命令

設置 SDRAM 模式

發送正常運行命令

系統啟動時,SDRAM 尚未初始化。理論上,程序在系統啟動后的任何時刻都可以進行 SDRAM 初始化。然而,由于 SDRAM 初始化過程比較復雜,使用的系統資源較多,SDRAM 初始化必須在所需的系統資源初始化完成后再進行。

具體上講,開發者在芯片剛剛啟動時(如 Reset_Handler 中)初始化 SDRAM 需要留心以下細節:

由于 SDRAM 初始化函數使用系統堆棧或全局變量,開發者必須確保系統堆棧或全局變量所在的物理內存上電及時鐘使能。

在程序跳轉到主程序啟動之前,全局變量未清零或初始化,如果在主函數之前執行 SDRAM 初始化,開發者必須手動初始化變量。

舉個例子,在 LPC5460x 中,開發者需要在 SystemInit 函數中初始化 SDRAM,該函數(SystemInit)由 Reset_Handler 調用。在調用系統初始化之前,要通過設置 AHBCLKCTRLSET0 寄存器將 SRAM 時鐘使能。

Reset_HandlerPROC EXPORTReset_Handler [WEAK] IMPORTSystemInitIMPORT__main ;clock control SRAM1/SRAM2/SRAM3 for stack LDRr0, = 0x40000220 ; AHBCLKCTRLSET0 MOVr1, #0x38 STRr1, [r0] LDRr0, =SystemInit BLXr0 LDRr0, =__main BXr0 ENDP

SDRAM 存儲器布局

當使用 SDRAM 時,外部存儲控制器(EMC)分配 SDRAM 一定的地址空間。開發者可以使用鏈接描述文件將代碼或數據分配到 SDRAM 中。值得注意的是,鏈接器腳本編程在不同 IDE 之間是不同的。

以 LPC5460x 系列微控制器為例,SDRAM 支持 4 個片選區,每個片選區最大支持 256MB 空間。

SDRAM 片選地址范圍

00xA0000000 - 0xA7FFFFFF

10xA8000000 - 0xAFFFFFFF

20xB0000000 - 0xB7FFFFFF

30xB8000000 - 0xBFFFFFFF

當 SDRAM 的硬件連接使用 SDRAM 片選 0 的情況下,在 KEIL 平臺下,將加載在 SPI FLASH 的 Coremark 基準測試程序拷貝到 SDRAM 中執行需要以下幾步。(coremark 基準測試程序包括 core_list_join.c,core_matrix.c,core_state.c 及 core_uTIl.c)。

定義 SDRAM 區域,從 0xA0000000 開始,大小為 0x80000。定義 SPI FLASH 區域,大小為 0x80000(SPI FLASH 存儲器的起始地址為 0x10000000)。

在 C 源碼中使用“SDRAM_Data” 和 “SDRAM_FuncTIon”屬性,標記放在 SDRAM 區域中的數據或程序。(SDRAM_Data 和 SDRAM_FuncTIon 只是文本名字)。

也可以將整個目標文件的數據和程序段配置到 SDRAM

# definem_spifi_start 0x10000000 # definem_spifi_size 0x800000 # definem_sdram_start 0xA0000000 # definem_sdram_size 0x80000 LR_m_text2 m_spifi_start m_spifi_size { ; load to SPIFI LR_m_sdram_text m_sdram_start m_sdram_size { *(SDRAM_Data) *(SDRAM_FuncTIon) core_list_join.o core_matrix.o core_state.o core_util.o }

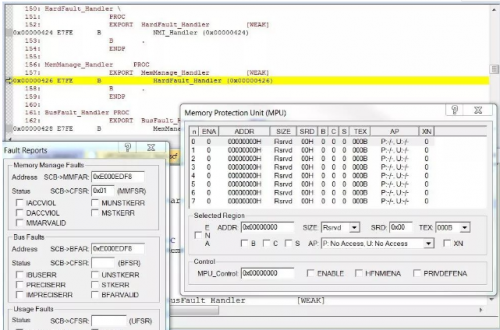

配置 MPU

在 SDRAM 中運行程序,開發者可能需要配置 ARM 內核內存保護單元(MPU)。

內存保護單元(MPU)是一個可編程單元,用于定義內存訪問權限。當 MPU 沒有使能時,內存地址空間具有默認的訪問權限。

如 ARM Cortex?-M4 器件通用用戶指南中所述,當程序執行 SDRAM 中的代碼且 SDRAM 內存影射地址的默認屬性為禁止執行時, 內核就會產生 HARDFAULT 異常,且指令訪問沖突標志 SCB-》CFSR 為 1,該異常表示處理器嘗試從不允許執行的位置獲取指令。

因此,當 SDRAM 被影射到默認不可執行的地址空間時(如在 LPC5460x 中,SDRAM 影射到 0xA0000000 起始的地址),開發者必須配置并使能 MPU 才能在 SDRAM 中執行代碼。如下例中,代碼配置并使能 MPU,允許從 0xA0000000 到 0xA0100000 的內存區域是可執行的。

MPU-》RNR = 0; //Region number 0 MPU-》RBAR = 0xA0000000; //Region base address/* Full Access | TEX: 000 | S: 0 | C: 0 | B:0 (No cacheable, no shareable)| 1M SIZE | ENABLE */ MPU-》RASR = ( 0《《 28) | ( 0x3《《 24) | ( 0x0《《 19) | ( 0《《 18) | ( 0《《 17) | ( 0《《 16) | ( 0xFF《 8) | ( 0x13《《 1) | ( 1《《 0); //Region size and enable MPU-》 CTRL= MPU_CTRL_ENABLE_Msk| MPU_CTRL_PRIVDEFENA_Msk;

SDRAM 性能基準

最后,小編在 LPC5460x 經過程序運行 CoreMark 性能基準測試,總結了一點點經驗,分享給大家

SDRAM(16 位帶寬)中的代碼執行效率僅為在內部 SRAM 中執行效率性能 40%,大約是內部 FLASH 中運行代碼性能的 50%;

代碼在 SDRAM 中運行時,較高的 CPU 頻率(CPU 沒有 Cache)不能改善執行效率,這時 SDRAM 帶寬成為系統性能的瓶頸。

基于這樣的測試結果,建議大家在要求較高性能時,把程序代碼放在內部 SRAM 執行,而用片外大容量的 SDRAM 存放海量的數據。