楊小平1,李永紅1,劉志剛1,2,嚴洪立1,李率真1

(1.成都信息工程大學 電子工程學院,四川 成都 610225;2.杭州旗捷科技有限公司,浙江 杭州310000)

摘要:提出了一種以FPGA和ARM處理器為核心的嵌入式多通道高速采集及脈沖提取系統設計的新方法。該系統主要應用于電力設備局部放電檢測,監測電力設備運行情況。系統主要實現用3種工作模式(正常工作模式、長記錄模式和觸發模式)實時采集、處理電信號,并根據采樣后得到的數據和脈沖波形來判斷被測信號是否正常工作。整個采集系統可實現100 MS/s的高速采樣,具有穩定性高、實時性強、易于擴展、便于攜帶等特點。

關鍵詞:多通道高速采集;脈沖提取;FPGA

0引言

數據采集,尤其是高速數據采集,在工業自動化控制、醫療器械、室內環境監測和軍事監控等領域已經得到了廣泛的應用。傳統的數據采集系統,通常是以單片機或者DSP為核心控制器,實現對數據信息的采集。隨著信息科技的發展,大眾對信息數據的實時性、穩定性等要求越來越高。而單片機的時鐘頻率較低、速度較慢并且軟件采用順序實現模式,從而使得數據采集速度低,進而影響整個系統的效率。雖然DSP有較高的運算處理速度,然而它很難完成對復雜外圍器件的控制。而FPGA(現場可編程門陣列)有單片機和DSP難以超越的優勢,FPGA時鐘頻率高、內部延時小、集成度高、全部控制邏輯由硬件完成、速度快、效率高[1]。

考慮到FPGA的諸多優勢,本文提出了一種以FPGA和ARM處理器為核心的嵌入式多通道高速采集及脈沖提取系統設計方案。系統有觸摸屏LCD和顯示器兩種顯示和下發配置命令方式。將該方案應用于電力設備局部放電檢測,通過采集和提取有效脈沖來實時監測電力設備的工作狀態。這一設計對安全用電及電力行業有重大的實用價值。

1系統總體結構

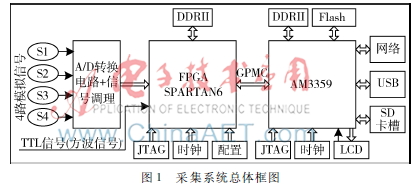

本數據采集系統基于FPGA+ARM架構。FPGA(XC6SLX75)外圍電路主要包括一個四通道100 MS/s采樣率、串行差分輸入輸出的AD(ADS6424),一片ARM(AM3359)控制器和一片DDR2(MT47H128M16)128 MB地址空間的存儲器,用于存儲采樣數據[2]。如圖1所示。

圖1中,S1~S4為4路模擬信號輸入端,為了得到較準確的脈沖信號,本設計使S1~S3作為信號輸入端,S4作為噪聲信號輸入端,通過前3路和第4路的比較進而有效地濾除噪聲。TTL信號作為相位信息,FPGA需要檢測是否有該同步信號并通知ARM。A/D轉換器前端的信號調理用來實現對輸入模擬信號的放大、衰減、濾波及輸入阻抗匹配,從而達到AD將模擬信號轉換成數字信號的要求。系統工作過程為:首先PC下發命令指令經ARM送到FPGA,配置FPGA的工作模式、采樣率等;其次,AD將轉換后的數字信號送給FPGA,FPGA經過運算處理提取有效脈沖信號存儲到DDR2中,然后向ARM發中斷命令,ARM通過GPMC總線提取DDR2中的數據;最后ARM通過網絡或USB將數據傳輸給PC顯示[3]。

2方案實現

2.1FPGA設計

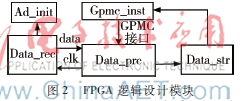

FPGA設計流程:系統上電后,FPGA首先初始化配置ADS6424芯片,然后將AD轉換后的數據由串行轉為并行再經過相應的算法處理得到有效的脈沖,將得到的脈沖存儲在DDR2中,再通過GPMC總線接口送給ARM。ARM控制器負責與用戶上位機程序通過網口或USB進行通信,給FPGA下達控制指令。根據上述流程以及FPGA要實現的功能,整個FPGA邏輯設計可劃分為5個模塊,分別為ADC初始化模塊Ad_init;ADC數據接收模塊Data_rec;ARM接口模塊 Gpmc_inst;數據處理模塊Data_prc;數據存儲模塊Data_str。如圖2所示。

2.1.1ADC初始化模塊Ad_init

ADC初始化模塊用于對ADS6424芯片進行復位及初始化配置來滿足AD正常工作,該模塊只在上電時或者系統復位時調用一次,并與Data_rec模塊協調工作用于600 Mb/s串行數據的低壓差分信號(LVDS)數據對位。

2.1.2數據輸入模塊Data_rec

數據輸入模塊接收ADC輸入的串行數據和時鐘,并將4路AD差分串行數據經SERDES(串并轉換器)轉換為并行數據發送給Data_prc模塊。Data_rec模塊與Data_prc模塊之間有FIFO用于同步AD采樣的100 MHz時鐘和FPGA內部處理數據的100 MHz時鐘。

2.1.3數據處理模塊Data_prc

數據處理模塊內部包含3個子模塊,分別用于三種工作狀態,各種工作狀態的數據和控制信號獨立,接口根據工作狀態選擇異步開關進行切換。

(1)正常工作狀態。正常工作情況下抗干擾脈沖提取算法如下:

①根據設置的閾值做背景噪聲的濾除;

②根據與噪聲通道的比較判斷是有用信號還是噪聲;

③判斷是否是方波信號,如果是方波信號則去除;

④將提取出的有用脈沖段及相位信息上傳給ARM。

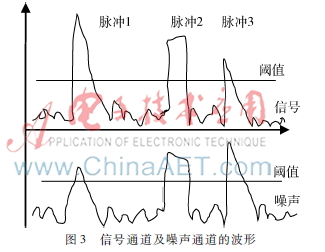

具體說明:根據設置的閾值得到脈沖1~3,對得到的脈沖段與噪聲通道做比較,只比較同相位的值,如果信號通道的值大于噪聲通道的值,則認為是有用信號,否則是噪聲,需要被濾除。如圖3所示,脈沖3的信號通道的值小于噪聲通道,需要被濾除。如果脈沖是方波,如脈沖2,也要被濾除。對提取出的有用的脈沖段如脈沖1,在傳輸至ARM時需要做如下處理:從第一個過閾值的點向前取55個點,向后取200個點,共取256個點,這樣保證取出來的脈沖段是一個完整的脈沖段[45]。

(2)長時間記錄。系統啟動后,根據輸入的時鐘和寫使能寫DDR2,將對應通道的AD采集數據輸入到FPGA,并對數據點數進行計數,達到30兆個數據點則停止存儲,并向ARM發送中斷信號。長記錄模式根據設置的采樣率和采樣時間,將采集到的點不做任何處理上傳給ARM,再通過ARM經由網絡上傳至PC,PC設置相關通道的閾值。長記錄采集模式的目的是得到各通道的背景噪聲值,方便設置閾值。

(3)觸發記錄。系統啟動后,根據輸入的時鐘和寫使能寫DDR2,達到一個時間長度則進行循環存儲。將輸入的數據進行逐點判斷,當達到觸發條件時,計算出讀取DDR2的首地址,并根據剩余采樣點數進行計數,達到采樣點數后則停止存儲,并向ARM發送中斷信號。

2.1.4指令解析模塊Gpmc_inst

采用100 MHz時鐘對ARM的Gpmc接口進行鎖存,解析ARM的輸入指令,并根據讀信號和地址信號返回寄存器的狀態值,或者DDR2存儲器內的數據。通過這個模塊與ARM進行通信。

2.1.5數據存儲模塊Data_str

該模塊負責DDR2存儲器的讀寫,采用MPMC的IP核,通過NPI接口進行控制,將輸入的16 bit數據字拼接成64 bit寬度寫入DDR2存儲器,輸出時根據讀使能信號取出DDR2中的數據,并將64 bit的數據拆成4個16 bit數據,按照順序輸出。數據存儲模塊沒有地址輸入接口,其內部只是簡單的地址遞加,當復位后,地址歸零。

2.2ARM設計

在該設計中ARM主要有兩個作用,一是擔當中間件,承上啟下,一方面接收PC命令,協議解析后配置給FPGA,另一方面將FPGA傳過來的數據,打包上傳給PC。傳輸支持USB和網絡兩種方式,USB包和UDP包采用相同的應用層協議。另一個是在不用PC的情況下,ARM作為上位機通過智能觸摸屏LCD顯示器下發命令配置FPGA,且FPGA也將采集到的數據和有效脈沖上傳給ARM,做相應的處理后通過LCD呈現。

2.2.1硬件部分

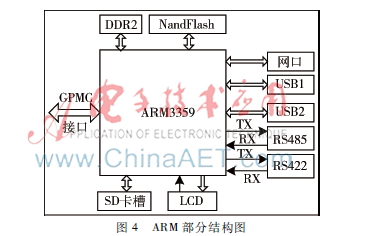

ARM部分結構如圖4所示。本設計采用兩種ARM啟動方式,一種是從SD卡啟動,另一種是從NandFlash啟動,兩種方式可通過撥碼開關切換。GPMC接口主要是連接FPGA和ARM,使其順利通信;DDR2起緩存數據作用;NandFlash用于存儲系統及應用文件等;ARM支持網口和USB1兩種方式與PC通信;USB2用于連接U盤將數據導出;觸摸屏LCD主要用于顯示波形和下發指令;預留RS485、RS422用于后期擴展功能[6]。

2.2.2應用部分

用QT(跨平臺的C++應用程序開發框架)開發設計GUI(圖形用戶界面),界面主要包括配置FPGA各種工作模式、設置采樣參數以及顯示有效脈沖等。如圖5所示。

3結論

本文給出了一種以FPGA+ARM處理器為核心的嵌入式多通道高速采集及脈沖提取系統設計的新方法,詳細闡述了系統設計流程和工作模式。經過長時間的測試和檢測,該系統可以實現數據的高速多通道采集及脈沖的提取。此設備可以應用于多種相關數據采集及分析的場合,有觸摸屏LCD和顯示器兩種顯示方式,具有穩定性高、實時性強、易于擴展、便于攜帶的特點。目前,該設備已應用于電力設備局部放電檢測,可以實現二維圖形顯示,后續將開發三維圖形顯示應用。

參考文獻

[1] 張偉,韓一明,吳新玲.基于FPGA的高速數據采集系統的設計[J].電力情報,2002,4(3):4649.

[2] 滕巖峰,周雪峰.帶USB 接口的100MHz高速數據采集系統的設計與實現[J].微計算機信息,2006,22(20):227229.

[3] 劉小林,范育兵,羅春暉.基于FPGA的多通道數據采集系統設計[J].電子技術應用,2009,35(7):4244.

[4] 徐文波,田耘.Xilinx FPGA開發使用教程(第2版)[M].北京:清華大學出版社,2012.

[5] 李宗海,陳蜀宇,李海偉.嵌入式Linux系統在ARM平臺上的構建[J].計算機系統應用,2010,19(10):153157.

[6] CORBET J, RUBINI A.Linux設備驅動程序(第三版)[M].魏永明,耿岳,鐘書毅,譯.北京:中國電力出版社,2006.