摘 要: 基于Atera公司的FPGA芯片對OmniVision圖像傳感器進行圖像采集前的準備工作,通過FPGA的GPIO端口模擬SCCB(串行攝像機控制總線)總線協議對傳感器的寄存器進行配置,從而完成對傳感器的初始化,使得攝像頭得以正常運行。

關鍵詞: FPGA;OmniVision圖像傳感器;SCCB

0 引言

視頻信號處理系統的前端部分是視頻圖像采集,是視頻監控、信息處理等系統的前端需要,對后端圖像處理系統的性能有著直接的影響。近年來,隨著通信技術和計算機技術的發展,人們對視頻采集的要求越來越高,正在向高速、高分辨率、高集成化、高可靠性方向發展。現場可編程門陣列(FPGA)具有規模大、集成度高、可靠性高等優點,對于視頻采集是非常理想的選擇與趨勢[1]。

OmniVision圖像傳感器具有獨有的傳感器技術,通過減少或消除光學或電子缺陷(如固定圖案噪聲、托尾、浮散等),提高圖像質量,得到清晰穩定的彩色圖像,并具有軟件可編程性,從而決定了此系列的傳感器應用越來越廣泛。傳感器正常工作的前提是對寄存器進行配置,使其按照需要的輸出方式、圖像質量和數據格式進行輸出,即對其初始化。OmniVision傳感器的初始化是通過SCCB總線協議的方式實現的,利用FPGA實現圖像采集的關鍵是在FPGA中實現SCCB總線協議[2-3]。

1 SCCB總線協議

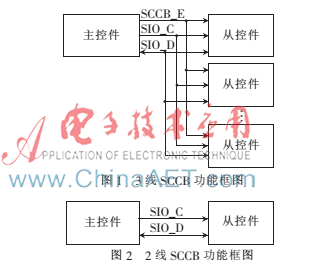

串行攝像機控制總線(Serial Camera Control Bus,SCCB)由OmniVision公司開發,廣泛應用于OV系列圖像傳感器上,是一種串行3線的總線,它由時鐘信號SIO_C、數據信號SIO_D和使能信號SCCB_E組成,可實現一個主器件對多個從器件的控制,如圖1所示。本文把芯片的引腳縮減為兩根,只用數據信號SIO_D和時鐘信號SIO_C,但是省去SCCB_E后的SCCB總線只能實現一個主器件對一個從器件的控制,如圖2所示。在本文中FPGA為主控件,OV系列傳感器為從器件[4]。

1.1 SCCB起始和終止時序

起始信號和終止信號都是由FPGA產生的,當SIO_C是高電平時,SIO_D從高電平轉到低電平時產生起始信號,如圖3所示;當SIO_C是高電平時,SIO_D從低電平轉到高電平時產生終止信號,如圖4所示。

1.2 SCCB寫時序

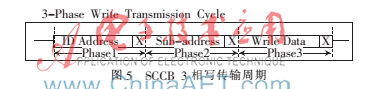

相(Phase)是SCCB進行數據傳遞的基本單位,一相由連續傳輸的8位數據與其后的第9位(共9位)組成。第9位在讀數據和寫數據時分別為自由位(Don′t care bit)和NA位(Ninth bit of a Read phase)。寫時序由3相構成,先寫設備地址,再寫寄存器地址,最后再寫需要配置的寄存器的數據,即ID-Address+SUB-Address+W-Data,如圖5所示。

1.3 SCCB數據傳輸有效性

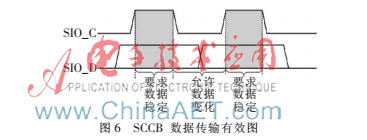

SCCB總線進行數據傳送時,SIO_C為高電平期間,SIO_D上的數據必須保持穩定,只有在SIO_C為低電平期間,SIO_D的高低電平狀態才允許變化。其時序圖如圖6所示。

2 模塊設計

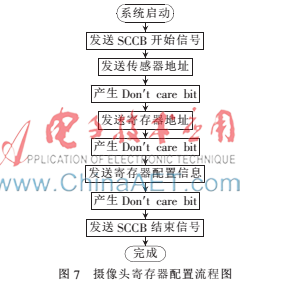

基于FPGA通過SCCB總線對OV7670初始化就是對攝像頭的寄存器進行配置,使其按照設定的輸出要求進行數據輸出[5]。攝像頭寄存器配置流程圖如圖7所示。SCCB控制模塊分為3個子模塊:分頻器、SCCB狀態控制模塊、數據查找表。這幾個模塊都是在QuartusII環境中用Verilog設計完成的。下面分別介紹這3個子模塊。

2.1 分頻器

由于系統時鐘頻率與SCCB控制模塊的數據傳輸頻率不一致,因此要對系統時鐘進行分頻達到SCCB總線模塊SIO_C的頻率,并且通過調整分頻模塊中的分頻系數來進行更換[6]。

2.2 SCCB狀態控制模塊

FPGA作為SCCB的主機,SCCB狀態控制模塊采用同步狀態機的設計方法來模擬SCCB的寫時序,從而完成對傳感器寄存器的配置。

2.3 數據查找表

將需要配置的傳感器寄存器地址和寄存器的配置數據都存放在數據查找表中,根據SCCB的時序規范順序送給SCCB狀態控制模塊。

3 硬件實現及仿真

硬件調試工作所選用的FPGA是Altera公司FPGA芯片,Verilog綜合及仿真平臺是QUARTUSII 13.0。將本實例中所設計的SCCB控制模塊的Verilog源代碼通過QuartusII編譯后,并在QuartusII環境下編寫TestBench文件,從而利用與Modelsim的無縫鏈接對SCCB總線模塊進行功能仿真。仿真波形如圖8所示,可以明確看出:當SIO_C位高時SIO_D由高變低時表明開始位;經過8位傳感器地址位、1位Don′t care、8位寄存器地址位、1位Don′t care、8位寄存器配置數據、1位Don′t care的數據傳輸;當SIO_C位高時SIO_D由低變高時表明結束,其時序符合SCCB總線時序規范。

4 結論

本文利用FPGA模擬SCCB總線的時序對OmniVision圖像傳感器的寄存器進行配置,使其可以按照特定的要求進行圖像輸出。該設計對OV系列的傳感器具有通用性,對圖像采集前端的設計具有重要意義。

參考文獻

[1] 方彩婷,葉盛,汪雪峰,等.基于FPGA的數字高清CMOS遙感成像技術[J].電子技術應用,2015,41(4):43-45.

[2] 苑瑋琦,湯永華.OmniVision圖像傳感器的SCCB總線協議在DSP中的實現[J].儀器儀表學報,2006(z2):1687-1688.

[3] OmniVision Serial Camera Control Bus(SCCB) Functional Specification, Document Version; 2.1[Z].www.vot.com.

[4] 張歡,汪紅,王芳芳.基于FPGA的實時圖像處理實驗平臺設計[J].微型機與應用,2014,33(11):26-28.

[5] 楊光耀.基于FPGA的圖像采集及處理系統設計[D].呼和浩特:內蒙古大學,2014.

[6] 陳景,李建華.基于FPGA的I2C讀寫控制器的設計與實現[J].自動化技術與應用,2010,29(2):86-88.