文獻標識碼: A

文章編號: 0258-7998(2014)08-0034-04

中文引用格式:楊大偉,李健.基于FPGA的實時視頻縮放算法設計實現[J].電子技術應用,2014,40(08):34-37.

目前視頻縮放系統大多采用視頻縮放的專業芯片設計,應用單一,靈活性差且成本較高[1]。視頻圖像是將豐富海量信息有效展示給大家的一種重要途徑。圖像的縮放是數字圖像處理中的基本操作,在視頻圖像傳輸、電影制作等有非常廣泛的應用。這項技術經常應用于匹配顯示器的分辨率,完整地顯示視頻圖像。本設計是在FPGA的平臺上以RAM_FIFO架構應用雙線性差值算法實現視頻圖像的任意比例的縮放,具有實行性好、處理速度快等特點。

1 雙線性算法的硬件的可行性

1.1 縮放算法的選取

典型的線性縮放算法有最近鄰域插值法、雙性插值縮放算法和雙三次插值縮放算法。最近領域插值法的計算復雜度較低,是以離待插值點最近的點的像素值作為待插值點的像素值。該算法計算量小,計算速度快,但是沒有考慮周圍像素點帶來的影響,僅僅將距離最近的像素點的值賦給當前像素點,簡單地將原圖像放大到指定大小。同時該算法硬件可實現性好,但是容易產生鋸齒狀和馬賽克現象,放大后的圖像有較明顯的失真。雙線性插值算法中待插值像素點的像素值由該像素點相鄰的4個像素點共同決定,由它們的像素值以及它們到插值點的距離加權求和得到。該插值算法能很好地解決最近鄰域插值算法帶來的鋸齒現象和馬賽克現象,顯示效果較好,但該算法具有低通濾波效果,會使圖像的邊緣模糊[2]。雙三次插值算法中待插值點的像素值是通過矩形網格中最近的16個采樣點的加權平均得到,在這里需要使用兩個多項式插值三次函數。該算法考慮了相鄰16個像素點的直接作用以及各點像素值的變化率等因素,效果比前兩種方式有大幅提升,改善了前兩種方式的不足,但是該算法的計算復雜度也大幅提升。

綜上所述,因為FPGA內部的邏輯資源有限,算法的復雜度越高,占用的邏輯資源就越多,硬件實現性差。因此綜合考慮顯示效果和硬件可實現性,實際工程中通常選用雙線性插值縮放算法。

1.2 雙線性差值算法原理

雙線性插值的本質是在兩個相互垂直的方向上分別進行線性插值,通過對兩個變量的插值函數進行擴展得到[3]。如圖1所示,設(u,v)是4個相鄰點(i,j)、(i+1,j)、(i,j+1)和(i+1,j+1)所圍成空間里的任意一點。在雙線性插值中,(u,v)點的像素值是由周圍4個相鄰點的像素值加權求和得出,假設g(i,j)、g(i+1,j)、g(i,j+1)和g(i+1,j+1)分別為4個相鄰像素點的像素值,則任意點(u,v)的像素值的求解過程如下所示:

g(i,j+u)=(g(i,j)-g(i,j+1))×u+g(i,j)(1)

g(i+1,j+u)=(g(i+1,j)-g(i+1,j+1))×u+g(i+1,j)(2)

g(i+v,j+u)=(g(i,j+u)-g(i+1,j+u))×v+g(i,j+u)(3)

2 雙線性插值縮放算法的硬件實現

雙線性插值縮放算法硬件實現總體框圖如圖1所示,該設計主要包括三大部分,分別為數據存儲、系數產生以及整體控制。

圖1 FPGA實現雙線性插值算法的結構框圖

2.1 數據存儲

由于該算法最少需要兩行數據才能進行運算,因此必須首先將輸入的視頻信號進行緩存,且至少緩存兩行以上的數據,才能運用待插值點所在位置的相鄰兩行中4個像素點的像素值算出待插值點的像素值。本設計采用了RAM_FIFO架構的存儲器進行數據緩存,該架構由多個雙口RAM構成(本設計中設為N個),每個RAM至少能存儲一行數據,將輸入的第一行、第二行視頻數據依次存入到第一個和第二個RAM中,依此類推。將接下來輸入的數據存入到其余的RAM中,當N個RAM存滿時,就停止往RAM中寫數據[4]。當數據存滿兩行后,根據縮放比例計算出當前輸出像素點映射到原圖像中的坐標位置,取計算結果的整數部分和整數部分加1,然后從存儲這兩行的兩個相鄰RAM中,分別通過兩個讀端口同時讀取相鄰地址的4個像素點的像素值,通過這4個像素值計算待插值點的像素值。當RAM中的數據被讀出以后,就可以往RAM中接著寫新的數據。其操作過程與一般FIFO的先進先出相似。另外,不同分辨率的刷新率不盡相同,為了實現任意比例的縮放并保證縮放前與縮放后數據同步,需要使用外部存儲器將輸入數據進行幀存儲,將輸入/輸出數據進行隔離,然后根據縮放算法的需要從外部存儲器中讀取數據進行縮放。

2.2 系數產生

在進行縮放算法時,首先得確定輸入和輸出的分辨率大小,通過輸入和輸出的分辨率確定縮放的比例,其計算如式(4)所示,式中xscale為水平方向縮放比例,yscale為垂直方向的縮放比例,inputxres、inputyres分別表示輸入視頻圖像水平方向和垂直方向的像素點個數。outputxres和outputyres分別表示縮放后輸出圖像的水平方向和垂直方向的像素點個數。

雙線性插值縮放算法的計算公式如下:

Dout=c1×x1+c2×x2+c3×x3+c4×x4(5)

式中,x1、x2、x3、x4分別為相鄰4個像素點(左上、右上、左下、右下)的像素值,可從存儲部分的RAM中讀出。因此只需求得插值系數c1、c2、c3、c4即可算出插值點的像素值,其計算公式如下:

c1=u×v

c2=(1-u)×vc3=u×(1-v)c4=(1-u)×(1-v) (6)

式中,u、v分別表示待插值點與原圖像中像素值為x1的像素點的水平距離和垂直距離。分別按照水平方向和垂直方向縮放比例計算出當前像素點在原圖像中的位置,分別取其計算結果的小數部分即為u和v,假設待插值點在縮放后的圖像中的坐標為(x,y),則u、v的計算公式如下:

u=x×xscale-[x×xscale]

v=y×yscale-[y×yscale] (7)

將式(4)帶入式(7)可以得出u、v的值,再將u、v代入式(6)中即可求得插值系數。最后將插值系數代入式(5)即可算出待插值點的像素值。

2.3 整體控制

縮放算法設計實現的流程如圖2所示,

圖2 FPGA實現雙線性插值算法的設計流程

整個縮放算法模塊采用較高分辨率的像素時鐘作為模塊的主控時鐘,采用輸出分辨率的幀同步信號作為模塊的復位信號。本模塊帶有裁剪功能,能夠對局部圖像進行放大,將數據存入RAM。本設計設定存滿2行后開始進行縮放,縮放包括地址映射、插值系數計算、加權求和等過程,最后將數據取整輸出,設計過程中需要保持插值系數計算和數據讀取的節拍一致。

3 仿真與驗證

本設計選用的主控芯片為Xilinx公司Spartan 6系列的xc6slx100-2fgg767[3],在ISE13.4開發平臺上運用Verilog HDL對各邏輯模塊進行設計,解碼芯片型號為SIL1161,編碼芯片的型號為CH7301,存儲器DDR2型號為MT47H32M16-25E,測試顯示器采用AOC 173P。

本設計輸入為實時的DVI接口,輸入分辨率為800×600,輸出分辨率為1 280×1 024,相對應的縮放比例xscale=1.60,yscale=1.71,刷新率為60 Hz。此設計適合切屏,若輸入的分辨率不同,則縮放比例、輸入的橫縱向點數均發生變化。當N=6時,適合全部輸入,相應的參數不發生變化。

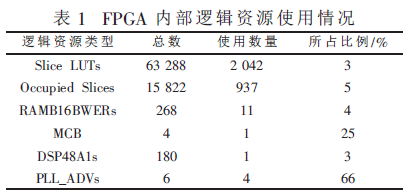

經驗證得到本設計占用FPGA內部主要邏輯資源情況如表1所示,支持的像素時鐘頻率高達108 MHz,對應分辨率為1 280×1 024。

圖3 縮放算法的仿真波形

圖3為在設計過程中通過ISE自帶仿真工具ISIM進行仿真得到的雙線性插值縮放算法的仿真圖。仿真圖中,iSiI1161_one_odck_G為輸入分辨率時鐘,iSiI1161_one_

qe[23:0]為輸入數據,calib_done 為DDR校準信號, clk_

scale為縮放核縮放時鐘,c1[50:0]為加權系數,inputXRes[10:0]、inputYRes[10:0]為輸入的橫、縱向像素點數,xScale[17:0]、yScale[17:0]為橫、縱向的縮放比例。

圖4 圖像切割放大拍攝效果圖

圖4為拍攝的實物效果圖,圖4(a)和4(b)將800×600的左半部份和右半部份分別放大到1 280×1 024。通過效果圖可知,本設計方案測試效果良好,適合于大屏幕實時拼接使用。

本文首先對常用的視頻圖像縮放算法進行介紹,綜合考慮硬件可實現性和縮放后顯示效果,最終選擇將雙線性插值縮放算法在FPGA上進行實現。本設計采用RAM_FIFO架構作為該算法硬件實現的核心思想,設計主要包括數據存儲、系數產生以及整體控制三大模塊。硬件實現結果表明,該設計達到了預期效果,畫面清晰穩定,無閃爍現象,能夠實現任意比例縮放,并且具有剪切功能,能實現局部放大。雙線性插值縮放算法處理會導致邊緣稍有模糊,但滿足人眼視覺需求,適合于工程應用。該設計能夠為大屏拼接、視頻的遠程傳輸等高速視頻信號處理提供必要的預處理裝置。

參考文獻

[1] 趙艷軍,何其銳,施錫濤.基于DVI和FPGA的視頻疊加器設計[J].電子技術應用,2011,37(6):31-34.

[2] 許錄平.數字圖像處理[M].北京:科學出版社,2007.

[3] Xilinx Inc.Spartan-6 family overview[EB/OL].(2010-03) [2014-04].http://www.xilinx.com.

[4] 徐文超,于意仲,柴耀龍,等.基于spartan-6 FPGA的DDR2控制器接口設計[J].數據采集與處理2012(27):167-171.

(收稿日期:2014-04-21)