0 引言

運算放大器是許多模擬系統(tǒng)和混合信號系統(tǒng)中的一個重要部分.高的直流增益無疑是運算放大器重要的設(shè)計指標(biāo).由于運算放大器一般用來實現(xiàn)一個反饋系統(tǒng),其開環(huán)直流增益的大小決定了使用運算放大器的反饋系統(tǒng)的精度.在現(xiàn)代CMOS模擬電路中,低壓差線性穩(wěn)壓器(LDO)的設(shè)計中,要求運算放大器有高的直流增益來減小其靜態(tài)誤差.折疊式共源共柵結(jié)構(gòu)可以提供高的增益,大的輸出電壓擺幅,好的頻率特性,而且功耗比較低.

本文根據(jù)設(shè)計要求,設(shè)計了一種采用增益提高技術(shù)的兩級放大器:第一級為在差分輸入單端輸出的折疊式共源共柵放大器中采用增益提高技術(shù)的低電壓電流鏡,以達(dá)到高增益且可提供適當(dāng)擺幅,第二級采用共源極電路結(jié)構(gòu)以增大輸出擺幅,同時提供適當(dāng)?shù)脑鲆?在放大器的兩級之間,采用改善零點頻率的密勒補償技術(shù)來使電路達(dá)到穩(wěn)定.經(jīng)過Cadence spectre軟件仿真顯示,該結(jié)構(gòu)直流增益達(dá)到了125.8 dB,相位裕度達(dá)到了61.2°.

1 運算放大器的設(shè)計

本文所設(shè)計的電路是在采用折疊式共源共柵結(jié)構(gòu)的兩級放大器中,采用增益提高技術(shù)的低電壓電流鏡來得到高增益.

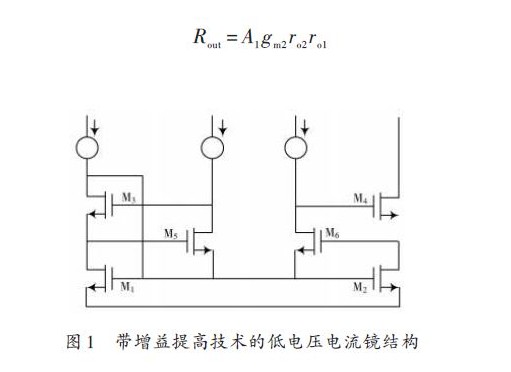

增益提高技術(shù)利用反饋技術(shù)來提高信號通路上的輸出阻抗,可以通過如圖1所示的結(jié)構(gòu)來說明.該結(jié)構(gòu)通過電流電壓反饋來控制M4 源端的電壓,使其保持恒定值,由于放大器M6 的作用,輸出電壓的變化對M2 漏端電壓的影響很小.通過M2 的電流變得恒定,從而產(chǎn)生更高的輸出阻抗.由小信號電路分析可知,該電路的輸出阻抗與傳統(tǒng)的共源共柵結(jié)構(gòu)相比,增加了A1 倍.

其輸出阻抗表達(dá)式為:

2 總電路結(jié)構(gòu)

圖2 為運算放大器的總電路結(jié)構(gòu):第一級采用PMOS管作為輸入管的折疊式共源共柵結(jié)構(gòu),并且在其增益提高級采用了增益提高技術(shù)來提高輸出阻抗,進(jìn)而提高增益.第二級采用簡單的共源級的典型結(jié)構(gòu)輸出,以提供最大的輸出擺幅.為使電路達(dá)到穩(wěn)定,在增益提高級與輸出之間采用了改善零點頻率的密勒補償.

電路的靜態(tài)工作條件由偏置電路提供.

2.1 輸入級電路結(jié)構(gòu)設(shè)計

在兩級運算放大器的設(shè)計中,第一級提供高增益;而在單級放大器中,折疊式共源共柵和套筒式共源共柵均可提供很高的增益.折疊式共源共柵運放與套筒式結(jié)構(gòu)相比,電壓的輸出擺幅較大些,而且在應(yīng)用方面輸入輸出可以短接,實現(xiàn)單位增益緩沖器;其次,折疊式共源共柵結(jié)構(gòu)的輸入共模范圍大,輸入共模電平可以接近VDD(NMOS作輸入管)或GND(PMOS作輸入管).若采用NMOS管作為輸入管,由于電子比空穴遷移率大,能得到更大的增益,但其折疊點有很大的寄生電容,影響了運放的速度,所以可采用PMOS管作為輸入管來提高主放大器的頻率特性.本文設(shè)計的差分輸入單端輸出的折疊式共源共柵結(jié)構(gòu)如圖3 所示,其中M1 ,M2 ,M5 ,M6 構(gòu)成折疊式差分電路;M3 ,M4 構(gòu)成差分電路的偏置電流源;M19 構(gòu)成差分輸入的尾電流源;M7 ,M8 ,M9 ,M10 構(gòu)成共源共柵電路;M13 ,M14 ,M15 ,M16 ,M17 ,M18 構(gòu)成增益提高電路,來提高第一級的輸出電阻.

Vbias1 ,Vbias2 ,Vbias3 提供增益提高級的直流偏置電壓.在第一級PMOS差分輸入的折疊式共源共柵中,增益提高技術(shù)的增益為:

運放第一級的增益為:Av1 = Gm *Rout ,Gm 為輸入差分管的跨導(dǎo).

2.2 輸出級電路結(jié)構(gòu)設(shè)計

第二級采用電流源負(fù)載的共源級電路,不僅可以提供很大的電壓增益,還可以提供大的輸出擺幅.在本文的設(shè)計中,如圖4所示,M11 作為第二級的輸入管,M12管提供偏置電流,其偏置電壓由Vbias3 提供.其增益為:

2.3 偏置電路結(jié)構(gòu)的設(shè)計

圖5 是本文所設(shè)計的偏置電路,Vbias1 為圖3 中輸入管的尾電流源M19 提供直流偏置電壓,Vbias2 為圖3中M5 ,M6 ,M7 ,M8 ,M15 ,M16 提供直流偏置電壓,Vbias3 為M3 ,M4 ,M12 提供直流偏置電壓.M20 ,M21 構(gòu)成電流鏡,理想電流源通過電流鏡將電流Iref 按管子的寬長比鏡像到M21 管,從而產(chǎn)生電路所需要的直流偏置電壓.

2.4 運算放大器整體電路結(jié)構(gòu)

圖6 為本文所設(shè)計的運算放大器的整體電路.各個端口定義為:VDD 為工作電壓;GND 為電源地;Vin1 為正相輸入端;Vin2 為反相輸入端;Vout 為輸出端;電阻Rm=1 kΩ,電容Cm=4 pF.Iref 為10 μA 的電流源.為了使在閉環(huán)電路中反饋運算放大器的輸入端的信號幅度和相位不使該信號在環(huán)路中產(chǎn)生振蕩,在電路的增益提高級和輸出級之間添加了密勒補償電容和補償電阻.電路的第一級為采用增益提高技術(shù)的共源共柵結(jié)構(gòu),其輸出電阻很大,所以主極點在第一級的輸出端.采用密勒補償電容Cm 把主極點向低頻移動,非主極點向高頻移動來實現(xiàn)極點分離.采用補償電阻Rm 來改善零點的頻率,從而使運算放大器達(dá)到穩(wěn)定.表1為整個運算放大器的各個管子的尺寸參數(shù).

3 電路仿真結(jié)果

采用Cadence公司的仿真工具spectre,仿真模型采用Chartered 0.35 μm,3.3 V 工藝BSIM3V3 模型對所設(shè)計的運算放大器進(jìn)行了仿真.增益和相位仿真結(jié)果如圖7所示,增益為125.8 dB,增益帶寬積為2.43 MHz,相位裕度為61.2°.

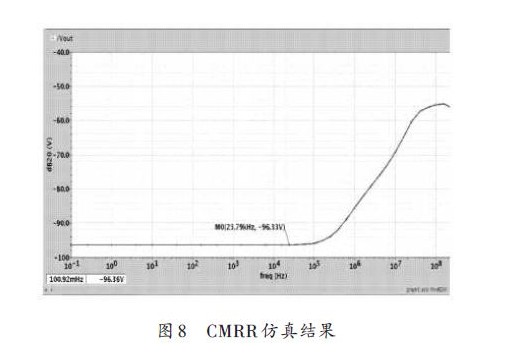

在仿真過程中,對CMRR 的仿真采用了簡化的仿真辦法,仿真的是實際數(shù)據(jù)的倒數(shù).從圖8 中可以看出,低頻共模抑制比(CMRR)為96.3 dB.

表2 為所設(shè)計的運算放大器與其他兩級運算放大器性能的比較.

4 結(jié)論

本文采用Cadence公司的仿真工具spectre,仿真模型采用chartered 0.35 μm 工藝對所設(shè)計的采用增益提高技術(shù)的折疊式共源共柵兩級放大器進(jìn)行了DC,AC及瞬態(tài)分析,仿真結(jié)果表明,本文所設(shè)計的兩級運算放大器具有125.8 dB的直流開環(huán)增益,與采用類似技術(shù)的其他放大器相比,其增益可達(dá)到最大.在1 pF的負(fù)載電容條件下,運放的單位增益帶寬積為2.43 MHz,相位裕度為61.2°,共模抑制比96.3 dB,使電路達(dá)到了穩(wěn)定狀態(tài),并且模擬結(jié)果達(dá)到了預(yù)期的效果.