基于Verilog計算精度可調的整數除法器的設計

摘要: 目前,實現除法器的方法有硬件實現和軟件實現兩種方法。硬件實現的方法主要是以硬件的消耗為代價,從而有實現速度快的特點。用硬件的方法來實現除法器的研究很多,如利用微處理器實現快速乘除法運算,FPGA實現二進制除法運算,模擬除法器等;而通過軟件實現的除法器算法,可以大大提高器件的工作頻率和設計的靈活性,可以從總體上提高設計性能,而設計高效實用的算法是除法器的關鍵,故除法器的算法研究成為現今熱點。

Abstract:

Key words :

除法器是電子技術領域的基礎模塊,在電子電路設計中得到廣泛應用。目前,實現除法器的方法有硬件實現和軟件實現兩種方法。硬件實現的方法主要是以硬件的消耗為代價,從而有實現速度快的特點。用硬件的方法來實現除法器的研究很多,如利用微處理器實現快速乘除法運算,FPGA實現二進制除法運算,模擬除法器等;而通過軟件實現的除法器算法,可以大大提高器件的工作頻率和設計的靈活性,可以從總體上提高設計性能,而設計高效實用的算法是除法器的關鍵,故除法器的算法研究成為現今熱點。

目前,軟件方面主要是通過減法算法來實現除法運算,把被除數作為被減數,除數作為減數,作減法,直到被減數小于減數為止,記錄能夠相減的次數即得到商的整數部分。將所得的余數乘以10作為被減數,除數作為減數,作減法,差重新置入被減數,反復相減,直到被減數小于減數為止,記錄能夠相減的次數即得到商的十分位數值。依此繼續下去,可得到商的百分位數值,千分位數值,……,要精確到哪一位,就依次做到哪一位。此方法的缺點是速度慢,而且最后一位的精度不高,為了克服以上的缺點,這里設計一種算法在軟件上改進了除法器運算的準確性和處理速度。

1 設計方法

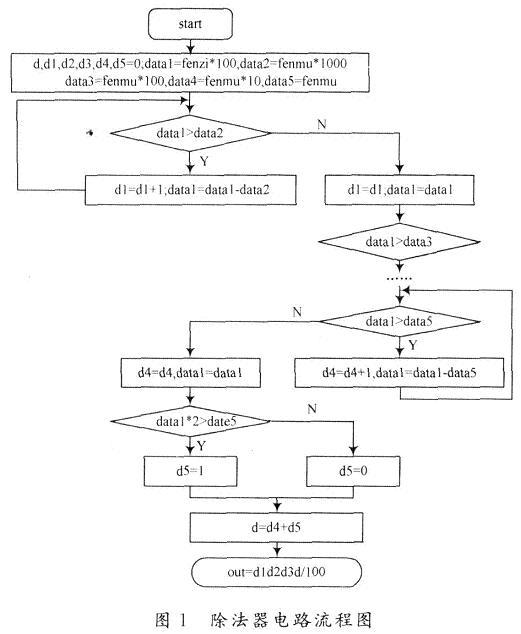

對于任意給定的兩個整數fenzi和fenmu,設fenzi為被除數,fenmu為除數。為了得到兩個數相除的十進制結果,本設計主要通過下面的算法來實現,假如要保留小數點后面的n位有效數字,首先把fenzi乘以10的n次方,賦值給寄存器變量dataO;接著把fenmu分別乘以10的(n+m),(n+m一1),(n+m一2),…,1,O次方分別賦值給(n+m+1)個不同的變量data(n+m+1),data(n+m),…,datal,其中m是fenzi和fenmu的位數之差(當fenzi的位數多于fenmu時,m為正,否則為負);先求出商的最高位的值,如果dataO大于data(n+m+1),則計數器自動加1,再把dataO和data(n+m+1)的差值賦給data0,再相減直到data0的值小于data(n+m+1),此時計數器的計數值就是最高位的值;依此用同樣的方法繼續下去,就可得到各個位上的值。對最后一位進行四舍五入處理,當相減后的dataO<datal時,再通過比較dataO*2是否大于datal,如果大于datal,則最后一位計數器的值加1,否則不變,最后把得到的整體值除以10的n次方,也就是小數點往左移動n位。傳統除法算法由于采用多次相減的過程來實現,相減的過程耗費了大量時鐘脈沖,而且對運算結果的最后一位沒有進行處理;而本設計是通過采用位擴展使除數和被除數位數相同,進而對每一位進行分開處理,減少了做減法運算的次數,從而提高運算速度;同時采用四舍五入的方法對運算結果進行處理,提高準確性。上面算法是一種順序方式,用Verilog硬件描述語言很容易實現,圖1為流程圖,其中假定fenzi為3位的整數,fenmu為2位的整數,除法運算精確到百分位。

2 仿真結果及分析

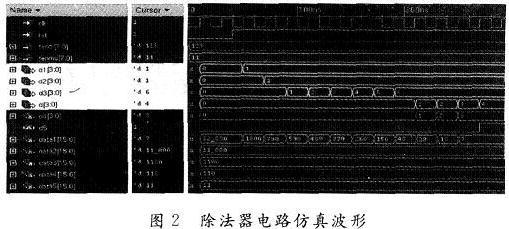

對上述的流程圖用Verilog描述語言編程,在Ca—dence的NC—Verilog仿真器下仿真,設輸入的Ienzi和fenmu的值分別為128和11,仿真波形如圖2所示。

從圖2的波形可以看出,輸出結果為1 164,除法運算要精確到百分位,所以往左移動2位,其最終的值為11.64,而實際的值為11.636 36……,經過四舍五入得到的結果完成正確。從仿真時間來看,對于相同的數值輸入,本設計只用了12個脈沖,而普通除法器至少需要20個脈沖(128/11=11余7,70/11=*,40/11=3余7,1l+6+3=20),相比之下本設計的除法算法有很大的優勢。

然而對于兩個位數相差很大的數相除,則本設計的速度優勢更加的明顯,本設計每一位的運行時間都不會超過9個時鐘脈沖,因此進行,z位計算的總脈沖也不會超過9n個,而傳統的除法運算需要多個時鐘脈沖,一般會是本設計時鐘脈沖的數倍。該算法同樣適合小數的運算,只要把小數化成整數,再做同樣的處理,就可以得到精確的結果。

3 結 語

通過對除法器算法的改進,用四舍五入的方法對數據進行處理,使得到的結果準確性有了進一步的提高;運用移位、循環減法,實現數據的高速運算,并能任意設定計算的精度。運用此方法在軟件方面設計除法器對速度和準確性的提高有積極意義。

此內容為AET網站原創,未經授權禁止轉載。