上次提出了一個處于異步時鐘域的MCU與FPGA直接通信的實現(xiàn)方式,其實在這之前,特權(quán)同學想列舉一個異步時鐘域中出現(xiàn)的很典型的問題。也就是要用一個反例來說明沒有足夠重視異步通信會給整個設(shè)計帶來什么樣的危害。

特權(quán)同學要舉的這個反例是真真切切的在某個項目上發(fā)生過的,很具有代表性。它不僅會涉及使用組合邏輯和時序邏輯在異步通信中的優(yōu)劣、而且能把亞穩(wěn)態(tài)的危害活生生的展現(xiàn)在你面前。

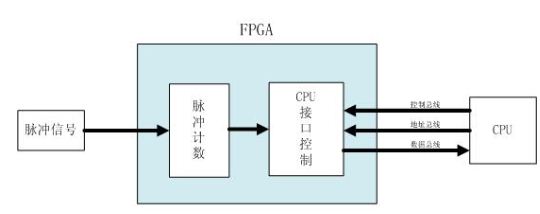

從這個模塊要實現(xiàn)的功能說起吧,如圖1所示,實現(xiàn)的功能其實很簡單的,就是一個頻率計,只不過FPGA除了脈沖采集進行計數(shù)外,還要響應(yīng)CPU的控制。

圖1 功能模塊

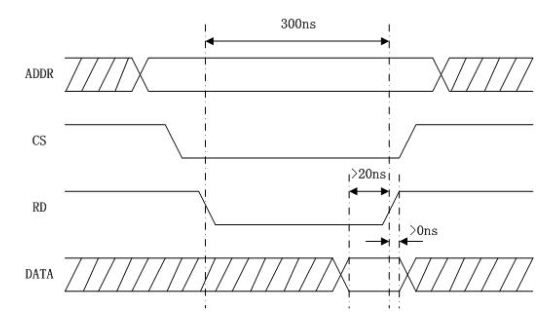

CPU的控制總線是指一個片選信號和一個讀選通信號,當二者都有效時,F(xiàn)PGA需要對CPU的地址總線進行譯碼,然后把采樣脈沖值送到CPU的數(shù)據(jù)總線上。

圖2 CPU讀時序

對于這樣“簡單”的功能,不少人可能會給出類似下面的以組合邏輯為主的實現(xiàn)方式:

input clk;

input rst_n;

input pulse;

input cs_n;

input rd_n;

input[3:0] addr_bus;

output reg[15:0] data_bus;

reg[15:0] counter;

always @(posedge pulse or negedge rst_n)

if(!rst_n) counter <= 16'd0;

else if(pulse) counter <= counter+1'b1;

wire dsp_cs = cs_n & rd_n;

always @(dsp_cs or addr_bus)

if(dsp_cs) data_bus <= 16'hzzzz;

else begin

case(addr_bus)

4'h0: data_bus <= counter;

4'h1: ……;

……

default: ;

endcase

end

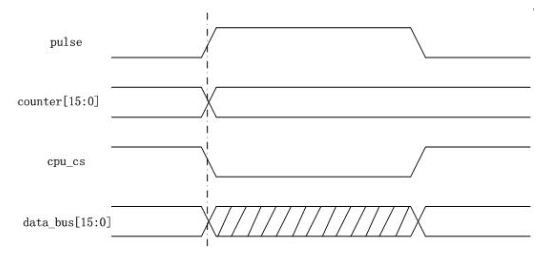

咋一看,可能你會覺得這個代碼也沒什么問題,功能似乎都實現(xiàn)了。而且你會覺得這個代碼簡潔,也不需要耗費多少邏輯就能實現(xiàn)。但是,對于這種時鐘滿天飛的設(shè)計,存在著諸多亞穩(wěn)態(tài)危害爆發(fā)的可能。脈沖信號和由CPU控制總線產(chǎn)生的選通信號是來自兩個異步時鐘域的信號。它們作為內(nèi)部的時鐘信號時,一個寫寄存器counter,一個讀寄存器counter。那么,很明顯的,存在著發(fā)生沖突的可能。換句話說,如果寄存器正處于改變狀態(tài)(被寫)時被讀取了,問題就隨著而來,如圖3所示。

圖3 數(shù)據(jù)沖突

脈沖信號pulse和CPU讀選通信號cpu_cs是異步信號,pulse什么時候出現(xiàn)上升沿和cpu_cs什么時候出現(xiàn)下降沿是不可控的。所以,如果它們很不幸的一起觸發(fā)了,那么,結(jié)果可想而知。計數(shù)器counter[15:0]正在加一,這個自增的過程還在進行中,CPU數(shù)據(jù)總線data_bus[15:0]來讀取counter[15:0],那么到底讀取的值是自增之前的值還是自增之后的值呢?或者是其它的值呢?

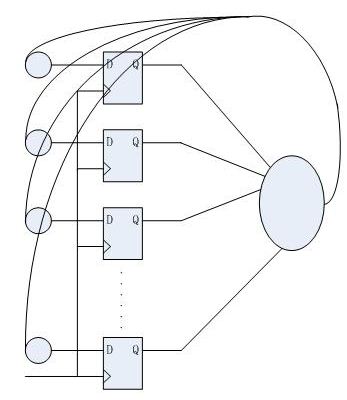

所示,它是一個計數(shù)器的近似模型。當計數(shù)器自增一的時候,如果最低位為0,那么自增的結(jié)果只會使最低位翻轉(zhuǎn);當最低位為1,那么自增一的后果除了使最低位翻轉(zhuǎn),還有可能使其它任何位翻轉(zhuǎn),比如4’b1111自增一的后果會使4個位都翻轉(zhuǎn)。由于每個位之間從發(fā)生翻轉(zhuǎn)到翻轉(zhuǎn)完成都需要經(jīng)過一段邏輯延時和走線延時,對于一個16位的計數(shù)器,要想使這16位寄存器的翻轉(zhuǎn)時間一致,那是不可能做到的。所以,對于之前的設(shè)計中出現(xiàn)了如圖3的沖突時,被讀取的脈沖值很可能是完全錯誤的。

圖4 計數(shù)器模型

上面的代碼是最典型的組合邏輯實現(xiàn)方式,是很不可行的。也許很多朋友會提出異議,也許還會提出很多類似的組合邏輯方案。但是,如果沒有同步設(shè)計的思想,不把這兩個異步時鐘域的信號同步到一個時鐘域里進行處理,沖突的問題在無法得到有效解決的。

那么,這個設(shè)計該如果同步呢?實現(xiàn)的方案其實上一次提到FPGA與MCU通信的博文里已經(jīng)給出了答案。它的設(shè)計思想可以如圖5所示。圖5先是使用脈沖檢測法把脈沖信號與系統(tǒng)時鐘信號clk同步,然后依然使用脈沖檢測法得到一個系統(tǒng)時鐘寬度的使能脈沖作為數(shù)據(jù)鎖存信號,也將CPU的控制信號和系統(tǒng)時鐘信號clk同步了。如此處理后,兩個異步時鐘域的信號就不存在任何讀寫沖突的情況了。

圖5 同步處理

這里提出來的解決方案就是使用了脈沖檢測法進行同步,還有一些其它的同步方式,譬如專用握手信號同步、異步FIFO等等。