EDA(ElectrONic Design Automation)即電子設計自動化技術,是指以計算機為基本工作平臺,把應用電子技術、計算機技術、智能化技術融合在一個電子CAD通用軟件包中,輔助進行三方面的電子設計工作,即集成電路設計、電子電路設計以及PCB設計。總之,EDA技術的基本特征是采用具有系統仿真和綜合能力的高級語言描述。它一般采用自頂向下的模塊化設計方法。但是由于所設計的數字系統的規模大小不一,且系統內部邏輯關系復雜,如何劃分邏輯功能模塊便成為設計數字系統的最重要的任務。

MAX+plus Ⅱ簡介

MAX+plus Ⅱ是一種與結構無關的全集成化設計環境,使設計者能對Altera的各種CPLD系列方便地進行設計輸入、快速處理和器件編程。MAX+plus Ⅱ開發系統具有強大的處理能力和高度的靈活性。其主要優點:與結構無關、多平臺、豐富的設計庫、開放的界面、全集成化、支持多種硬件描述語言(HDL)等。

設計流程

數字系統的設計采用自頂向下、由粗到細,逐步分解的設計方法,最頂層電路是指系統的整體要求,最下層是具體的邏輯電路的實現。自頂向下的設計方法將一個復雜的系統逐漸分解成若干功能模塊,從而進行設計描述,并且應用EDA軟件平臺自動完成各功能模塊的邏輯綜合與優化,門級電路的布局,再下載到硬件中實現設計。利用MAX+plus II進行電路設計的一般流程如圖1所示。

MAX+plusⅡ開發平臺的EDA設計方法" src="http://files.chinaaet.com/images/20110922/e4f7e0da-154e-47bf-b0f0-24907a6f1e72.jpg" />

具體設計過程如下。

1)設計輸入。MAX+plus Ⅱ支持多種設計輸入方式,如原理圖輸入、波形輸入、文本輸入和它們的混合輸入。

2)設計處理。設計輸入完后,用MAX+plus Ⅱ的編譯器編譯、查錯、修改直到設計輸入正確,同時將對輸入文件進行邏輯簡化、優化,最后生成一個編程文件。這是設計的核心環節。

3)設計檢查。MAX+plus Ⅱ為設計者提供完善的檢查方法設計仿真和定時分析。其目的是檢驗電路的邏輯功能是否正確,同時測試目標器件在最差情況下的時延。這一查錯過程對于檢驗組合邏輯電路的競爭冒險和時序邏輯電路的時序、時延等至關重要。

4)器件編程。當電路設計、校驗之后,MAX+plus Ⅱ的Programmer將編譯器所生成的編譯文件下載到具體的CPLD器件中,即實現目標器件的物理編程。

文本輸入方式和圖形輸入方式設計一個模60計數器

系統分析

模60計數器是可由一個10進制計數器和一個異步清零6進制計數器組成的。本設計采用10進制計數器74160組件和6進制計數器組成。數字系統分塊后,需要選擇正確描述系統邏輯功能的方式。對于所選用的CPLD,需要用相應的設計開發軟件。如MAX+plus Ⅱ的設計描述方式有文本、波形、圖形多種方式。圖形輸入方式直觀易懂。當系統較大時,由于此方式連線多,使用十分不方便。采用VHDL硬件描述語言的描述方式與結構無關,設計難度降低,軟件修改方便而且大部分受控功能模塊已經編譯驗證,系統設計時只要選擇這些模塊并按一定的邏輯功能組合即可。

系統設計

本設計6進制計數器采用文本輸入方式設計,其代碼如下:

LIBRARY ieee ;

USE ieee. STd_LOGIC_1164. all ;

USE ieee. std_logic_unsigned. all ;

ENTITY counter6 IS %定義模塊IS

PORT (Load,En Clrn,Clk:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(2 downto 0) ;

%定義輸入端口

Q:OU T STD_LOGIC_VECTOR(2 downto 0) ;

%定義輸出端口

Co:OU T STD_LOGIC)

END counter6 ;

ARCHITECTURE a OF counter6 IS

BEGIN %定義過程

PROCESS(Clk)

variable tmp:std_logic_vector (2 downto 0) ;

%定義一個矢量

begin

IF Clrn =’0’THEN tmp:= "000" ;

else

IF( Clk’event AND Clk =’1’) THEN %過程聲明

IF Load =’0’THEN tmp:= D ;

ELSIF En =’1’THEN

IF tmp = "101" THEN tmp:= "000" ;

ELSE tmp:= tmp + 1 ;

END IF ;

END IF ;

END IF ;

END IF ;

Q < = tmp ; Co < = (tmp (0) AND tmp (2) AND En) ;

END PROCESS ;

END a ;

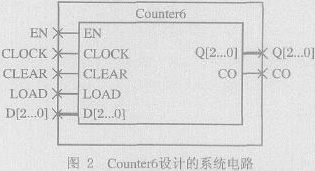

保存并編譯設計代碼,然后創建電路符號counter6,接著用圖形輸入方式編輯模60計數器,在編輯的過程當中可以引用6進制電路符號counter6。設計的系統電路如圖2所示。

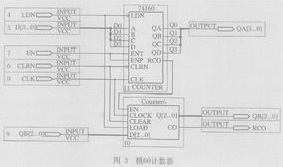

模60計數器由十進制計數器74160和以上設計的六進制計數器組成(見圖3),當74160計到9時,產生進位使6進制電路能計數。

系統仿真

為了保證設計的正確性,系統設計之后還要進行仿真。本系統采用MAX7000S系列CPLD芯片,應用MAX+plus Ⅱ對各種文件從底層到頂層逐個編譯,再進行邏輯仿真。其仿真波形如圖4所示。仿真之后通過MAX+plus Ⅱ的Programmer下載到可編程芯片上便完成設計。利用MAX+plusⅡ編譯、查錯生成一個能實現模60的計數器,從圖4可見初值為58,使能端EN和清除控制端CLRN為高電平。經過兩個時鐘周期上升沿Qa從8變到0,Qb從5變到0,再開始新一輪的計數。

結束語

數字電路系統設計采用先進的EDA軟件和硬件描述語言,借助于CPLD實現設計,體現了數字電路設計系統芯片化。芯片系統化的設計化思想使設計者根據自己的實際需要構造邏輯功能的數字集成電路變得簡捷。

作者:趙大興 彭章明 丁建軍 湖北工業大學機械工程學院 來源:湖北工業大學學報