摘要:現有變電站改造成數字化變電站時需要增加過程層設備,其中對刀閘接口控制箱的動作可靠性提出了極高的要求。提出一種基于雙FPGA實現多重邏輯閉鎖的刀閘接口控制箱實現方案。設計了FPGA電源和時鐘實現電路,兩塊FPGA的信息交換方式以及邏輯互鎖方法。詳細描述了出口電路自檢方案。介紹FPGA配置和編程方法,給出了FPGA的時序仿真。測試了電源建立波形,實現并驗證了裝置運行的可靠性。該方案能夠有效防止誤動作發生,適用于有此需求的一般裝置。

關鍵詞:FPGA;數字化變電站;刀閘接口箱;出口閉鎖;回路自檢

數字化變電站的核心思想是設備智能化、信息互動化、控制網絡化、功能一體化、狀態可視化,最終實現高可靠的堅強智能電網。數字化變電站與傳統變電站相比在間隔層和一次設備之間增加了一個強大的過程層業務單元,可以把現有一次設備接入數字化變電站。過程層主要設備為智能接口單元:包含斷路器操作箱和刀閘接口控制箱,本文介紹刀閘接口控制箱的實現。

刀閘接口箱用來控制隔離開關,其可靠性成為數字化站檢修的關鍵部位,因此需要設計一種高可靠裝置以防止帶負荷拉、合隔離開關,帶電合接地刀閘,帶接地線(接地刀閘)合斷路器(隔離開關)。裝置還要滿足智能控制、通訊以保障符合IEC61850標準運行。本文介紹利用雙FPGA實現刀閘接口箱的高可靠性以及通訊控制的設計方法。

1 系統設計

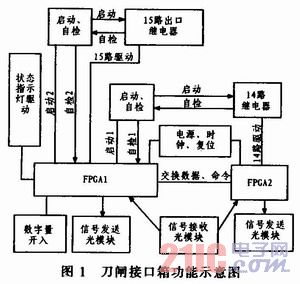

一個220 kV斷路器需要7個隔離刀閘,一個隔離刀閘需要6個開關量采集點以及1組帶閉鎖的組合觸點。6個開關量分別用于采集三相刀閘的的開和關位置信息。刀閘接口控制箱除實現上述功能外,還具備信號指示燈控制、多種自檢功能、通訊控制、現場狀態信號采集和上傳、上級控制命令接收、解析、執行等,其功能框圖如圖1所示。為了實現高可靠性控制,邏輯上采用了雙FPGA控制,驅動電路上采用獨立雙啟動,采用多繼電器“邏輯與”組合實現出口控制。防止刀閘檢修時隔離開關誤閉合導致人員傷亡事件發生。

1.1 硬件實現方案

數字量開入用于采集現場信號狀態和邏輯控制硬壓板,開入電路均具備一定的抗干擾能力;出口電路具備7路分閘、7路合閘以及7路閉鎖用于執行相應的回路分閘與合閘。開入和出口均有強弱電隔離回路,能夠保障4級快速瞬變和浪涌4級抗擾度實驗。光收發通道用于實現遠動控制,實現現場數據和裝置狀態量上傳和接收控制命令,實現刀閘分合操作。還有14路指示燈用于指示分合閘位置和裝置運行狀態。裝置還有一個CPU單元用于數據運算和解析執行命令。CPU單元與第一個FPGA之間通過串口交換數據,通過GPIO與第二個FPGA交換數據和命令。兩塊FPGA獨立啟動和出口;然后再把出口繼電器觸點進行邏輯組合實現更高等級的可靠傳動。出口自檢回路包括啟動自檢、擊穿自檢和斷線自檢。其中啟動和斷線故障立即報警,擊穿故障時立即閉鎖出口。硬件設計的核心為兩塊相同的FPGA,該裝置的所有邏輯功能都是利用這兩塊FPGA芯片實現。該芯片選用XILINX的XC3S50AN,擁有50 k個系統門、1 584個邏輯單元、1 MbitFlashROM、65 KRAM、3個乘法器、2個DCM時鐘管理器;最大可提供144個IO口。該芯片還具有低功耗、靈活的信號電平兼容性;內核1.2 V、IO為3.3 VTTL支持5 V容限輸入。PU單元采用具備串口和GPIO的單元,限于篇幅這里不作介紹,本方案重點是采用先進的出口自檢、啟動以及出口邏輯組合;FPGA的系統設計方案:電源管理、復位電路、時鐘分配以及FPGA配置電路的設計。

1.2 電源、復位及時鐘系統的設計方案

本裝置需要以下等級電源:24 V電源為出口繼電器提供驅動、5 V電源為光信號收發模塊提供驅動、3.3 V電源為FPGA的IO、時鐘電路提供驅動電源、1.2 V為FPGA內核提供工作電源。選用免維護的LAMDA電源模塊HWS50/HD把直流220 V轉換為+24 V;DC—DC模塊PSS3—24—5把+24 V轉換到+5 V。FPGA所需要的3.3 V和1.2 V則選用高效電源管理芯片ISL6410AIU和MIC39101—3.3BM,其實現方法如圖2所示。U1-4腳為1.2 V電源建立完成標志,使用該信號控制U2-1腳3.3 V電源使能,保證內核電源可靠工作后再建立IO電源。L1為濾波電感器,應保證負載的通流能力,選用coilcraft公司的DO1813H—153MLD型號。選用高可靠性的集成電路ADM6711TAKS實現手動復位和電平門檻監視復位。復位輸出信號PORESET#為低電平有效,保障整個系統可靠復位。選用epson公司的高精度低溫漂晶體振蕩器OCETGLJ-16 M,所需電源為3.3 V,輸出時鐘為16 MHz,連接到FPGA的全局時鐘入口,可以直接驅動兩個FPGA。

1.3 啟動、出口及自檢回路

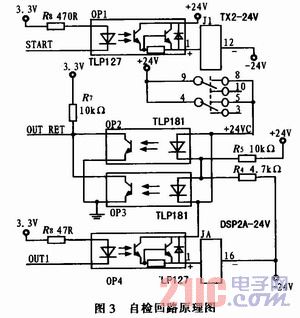

為了實現出口閉鎖,設計了出口啟動電路,只有出口電路和啟動電路同時動作時才能把信號開出。為了防止電路故障而導致拒動,設計了啟動及出口回路的自檢電路如圖3所示。兩個FPGA各有一套完整的啟動及自檢回路,組合出口是利用兩個FPGA驅動的繼電器觸點進行“邏輯與”后實現出口。啟動自檢方法:關閉出口信號(OUT1高電平),打開啟動繼電器(START低電平);OP1導通,J1動作+24VC接通24 V電源、OP2導通,OUT_RET變為低電平,實現啟動自檢。出口自檢方法:關閉啟動繼電器(START高電平),打開出口(OUT1低電平);OP3、OP4導通,OUT_ RET變為低電平,實現出口回路自檢。多路出口自檢時,需要每一路輪流自檢,由于可能會有干擾,可以通過設定某一路10輪自檢均錯誤時才判定該回路故障。

2 FPGA編程

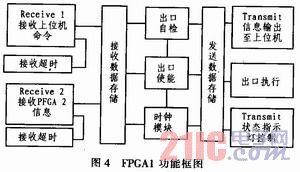

本方案由于沒有主控單元(MCU),需要接受上位機的指令并執行相應功能。所以出口控制的實現都要依賴于FPGA,在每個FPGA中均設計啟動和出口自檢以及數據交換處理功能,功能如圖4所示,第二塊FPGA可以參考第一塊設計,FPGA2通過串口把自己的狀態提供給FPGA1,兩塊FPGA均是通過接收上位機的命令執行相應的功能。

2.1 信息收發模塊

信息收發模塊:主要有命令接收、信息發送回路,在FPGA中做一個異步接收器、串并轉換器件,把接收到的數據存入命令緩沖區。把現場的狀態信息通過開入回路采集后存入狀態緩沖區,當收到回傳信息命令后把信息數據轉換為串行格式通過光發送模塊送出數據。功能框圖如圖5所示。

2.2 命令執行模塊

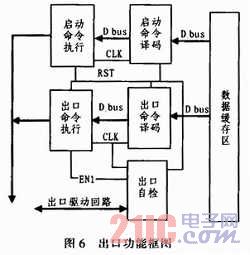

命令執行模塊包括:出口啟動、出口使能、出口傳動功能。命令執行電路讀取存放在信息緩存中命令數據,接收到啟動命令時,啟動出口電源,為隨時出口做準備,其間沒有出口命令并且啟動故障消失時,啟動返回。當接收到出口命令時,執行出口命令;啟動及出口命令發出后,通過硬件執行電路驅動隔離開關閉合或斷開。并把執行結果存入狀態信息緩存。功能框圖如圖6所示。

2.3 時鐘生成模塊

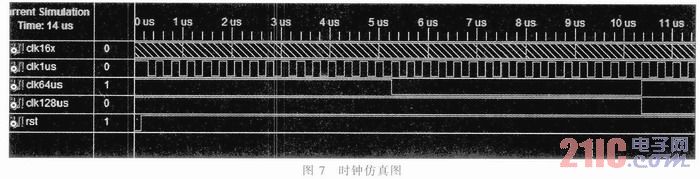

時鐘生成模塊在實現出口自檢、使能時需要1μs、64μs和128μs的時鐘,實現指示燈閃爍時需要500μs時鐘。利用FPGA的DMC模塊把16 MHz的時鐘分成系統所需的時鐘。時鐘仿真圖如圖7所示。

2.4 軟件實現方案及編程

軟件編程按照分層模塊的方式進行,采用常用的硬件編程語言VHDL;兩塊FPGA獨立編譯分別下載,保證邏輯和實現的獨立性。編譯環境為XILINX的免費軟件ISE軟件,版本號位10.3.1,該軟件有非常強大的功能,具備很多常用的IP核,可以直接加載。自帶仿真軟件可以實現邏輯和時序仿真。配合XILINX的另一款邏輯分析軟件chipscope可以在線探測芯片實際運行狀態,測試邏輯和時序錯誤。綜合使用軟件能夠快速實現系統設計。軟件功能框圖已經給出,限于篇幅VHDL語言的程序代碼不再給出。

3 程序下載及配置方案

本系統兩塊FPGA全部使用ISP方案,利用FPGA的JTAG接口,把編程數據下載到內部的FLASMROM內。XC3S50AN的配置模式控制管腳M2、M1、M0決定FPGA引導配置數據的方法,計有8種。系統上電時,給PROG_B一個低電平,觸發一次數據配置,在INIT_B低電平期間讀取M2:M1:M0狀態決定數據引導方式。本系統選用INTERNAL MASTER SPI MODE[0:1:1]。其中方便調試的JTAG MODE[1:0:1]可以支持JTAG口直接配置FPAG數據用于帶電調試,當斷電后數據丟失。XC3S50AN參與配置的管腳及功能如表1所示。

本設計為保證可靠性選用了2塊FPGA同時工作,它們之間通過模擬串行口交換信息可以實現相互邏輯上閉鎖。在電路出口處把2塊FPGA驅動的繼電器觸點串聯后作為最終的出口控制,又在硬體電路上實現邏輯閉鎖。如此可以保證裝置的可靠動作,不會再有誤動作發生。

4 整體測試

該方案設計的刀閘接口控制箱單元,已經制成產品調試成功,并完成型式試驗。在數字化變電站試運行,運行中沒有發現問題。測試環節進行了以下測試。

4.1 單板硬件測試

主要測試電源系統工作電壓值及上電時序如圖8所示,通道1至3分別為1.2、5、3.3 V電壓建立波形,對于FPGA要求內核電源1.2 V建立完成后才能允許IO模塊電源3.3 V建立。圖9中通道4為3.3 V電源。通道1為FPGA程序引導完成信號DONE,DONE完成后FPGA內部邏輯可以正常工作。通道3為上電復位信號,該信號復位期間所有邏輯信號處在復位狀態,完成復位后系統就可以正常工作了。

4.2 FPGA功能測試

一般通過仿真和黑盒測試兩種方法,每一個功能模塊可以通過設定邊界條件測試功能完整性,整體邏輯功能一般通過測試輸入信號和輸出信號的邏輯關系,然后測試整套裝置的功能完整性。

4.3 整裝置功能和性能測試

整套裝置按照設計技術指標測試功能和性能,主要測試了開關量動作值、動作時間、分辨率,光口通訊測試以及整裝置環境適應性和EMC電磁兼容測試。均達到了設計要求,已經通過試驗,滿足現場運行條件。

5 結束語

由于方案應用了軟體邏輯和出口驅動電路雙重閉鎖,使裝置的運行可靠性有了很大提高,誤動的可能性降到極小。測試和現場運行證明該方案是可靠的。該方案可推廣到其他對動作可靠性要求高的場合。但是該方案為提高動作可靠性而增加了相對冗余的軟件邏輯和硬件資源,必將提高系統制造成本。