本文給出的視頻采集和顯示模塊在設計時,選取分辨率為768×494像素的NTSC制式, 并選用輸出像素為640×480的CCD攝像頭; FPGA選取Altera CycloneⅡ系列Ep2c35F672c36 (內含35000個邏輯單元); 主動串行配置器件為Epcs16; 可配置VGA DAC ADV7123 ( 內含3 個10 位高速DAC)及VGA輸出口, 同時支持NTSC和PAL制式的視頻解碼器ADV7181及RCA視頻輸入接口。

1 ADV7181的特性及其寄存器配置

ADV7181是一款集成的視頻解碼器, 可支持多種格式的模擬視頻信號輸入, 包括CVBS,S_VIDEO 和YPrPb 分量, 并可自動檢測NTSC、PAL 和SECAM。ADV7181 可輸出16 位或8 位與CCIR656標準兼容的YCrCb 4:2: 2視頻數據, 包括VS、HS、Blank等重要信號。由于該器件功能強大, 因此, 要正確使用這款芯片, 就必須對其內部240個寄存器進行合理配置。本系統只需設計I2C_Controller模塊和I2C_AV_config模塊對其中的40個寄存器進行參數配置即可。

1.1 I2C_Controller模塊設計

I2C_Controller使用33個I2C時鐘周期來完成1次24位數據, 其中第1個時鐘周期用于初始化控制器, 第2~3個周期用于啟動傳輸, 第4~30個周期用于傳輸數據(其中包括24為數據和3個ACK),最后3 個周期用于停止傳輸。在程序當中,SD_counter用于對傳輸進行計數, 并控制數據的傳輸。

1.2 I2C_AV_config模塊設計

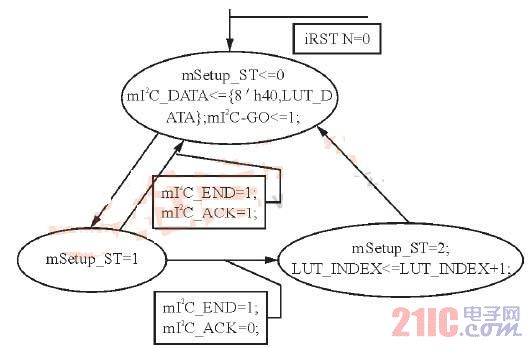

該模塊中的每個寄存器配置需要三步。一般用mSetup_ST表示當前進行到哪一步, mI2C_GO=1表示啟動I2C傳輸, mI2C_END=1表示I2C傳輸結束, mI2C_ACK=0表示應答信號有效。圖1所示是該寄存器的配置狀態圖。

圖1 寄存器配置狀態圖

在圖1中, 復位信號一旦有效, 即表明對寄存器的配置進入到第一步, 此時8位從設備地址、8位寄存器地址和8位數據進行連接, 以組成24位傳輸數據; 接著啟動I2C 傳輸, 進入第二步( mSetup_ST =1) , 此后一旦檢測到傳輸結束(mI2C_END=1), 便對應答信號mI2C_ACK進行判斷, 如果應答有效, 則進入下一步mSetup_ST=2,否則返回到mSetup_ST=0, 重新傳輸數據。

2 圖像采集和Video_to_VGA模塊設計

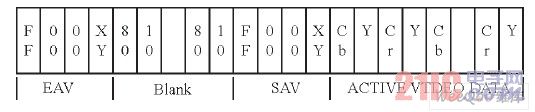

由ADV7181輸出的itu_r65*:2:2格式的視頻數據流格式如圖2所示。圖中, EAV和SAV為兩個基準信號, 要想獲得有效視頻數據, 就得首先檢測到SAV。操作時, 首先要對FF0000進行檢測, 然后再根據XY提取F、H來判斷SAV基準信號。XY一般由8位數據組成, 圖3所示是其位格式表示。

圖2 itu_r65*:2:2格式視頻數據流

圖3 XY各位表示

2.1 ITU_R656_DECODER模塊設計

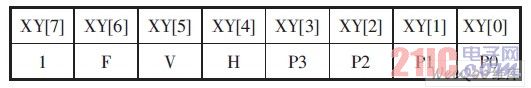

圖3中, XY的第七位為場信號, F為0表示第一場, F為1表示第二場; XY的第六位為場消隱信號, V為0表示數據是有效信號, V為1表示數據處于場消隱階段; XY的第五位為有效數據開始結束信號, H為0表示有效視頻數據開始信號,H為1表示有效視頻數據結束; 而P0、P1、P2、P3為保護比特。操作時首先要檢測FF 00 00, 然后提取F、V、H等信號, 最后再根據這些信號信息對視頻數據進行相應的處理。圖4所示是本圖像采集系統的總體框圖。

圖4 系統總體框圖

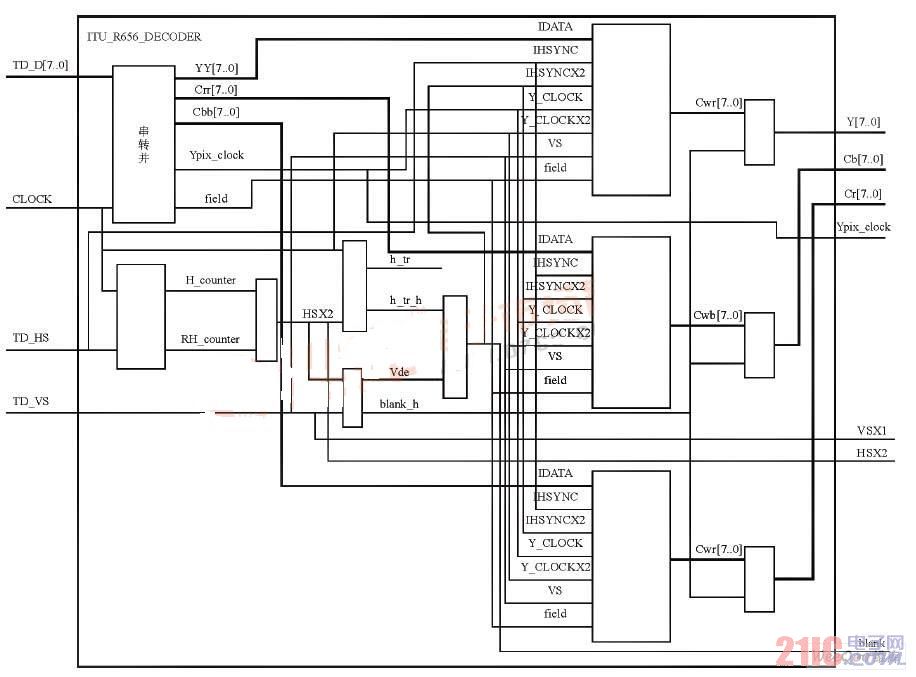

Video_to_VGA 模塊主要由ITU_R656_DECODER模塊和YCbCr2RGB模塊組成, 這里先對ITU_R656_DECODER模塊進行設計。圖5所示是ITU_R656_DECODER模塊的設計原理框圖。

設計時, 首先應構建串轉并模塊, 以便對有效信號中的串行YCbCr信號進行分離, 然后對亮度色差信號分別進行處理, 以同時產生field和13.5M的Ypix_clock信號; 接著對TD_HS進行倍頻以產生HSX2, 再通過三個dui_port_c1024模塊將4:2:2的視頻信號轉換為4:4:4的視頻信號。其中,在dui_port_c1024模塊中使用乒乓操作, 以實現對數據的連續處理, 讀時鐘為寫時鐘的2倍, 即寫入一行數據, 讀出后變為兩行, 這樣可實現奇行代替偶行, 從而實現去交織(由于人眼對奇行偶行數據分辨力較差, 故允許這種處理方式),輸出的Y, Cb, Cr用于后期所要使用的10位RGB信號, 而Ypix_clock、HSX2和VSX1則用于產生VGA的時序信號。

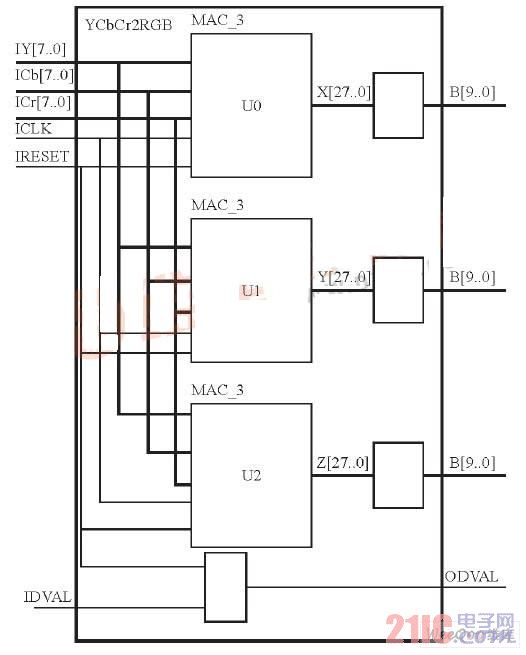

2.2 YCbCr2RGB模塊設計

該模塊實際上用于完成一個色度空間的轉換功能, 它可將Y, Cb, Cr信號轉換為所要使用的10位RGB信號。其轉換關系如下:

R=1.164 (Y-16) +1.596 (Cr-128)

G =1.164 ( Y -16) -0.813 ( Cr -128) -0.392(Cb-128)

B=1.164 (Y-16) +2.017 (Cb-128)

這樣, 就可用3個MAC_3模塊分別完成對R、G、B信號的轉換, 圖6所示是其轉換原理框圖。

圖5 ITU_R656_DECODER模塊原理框圖

圖6 YCbCr2RGB模塊轉換原理框圖

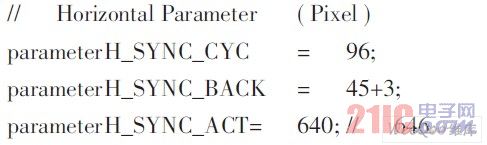

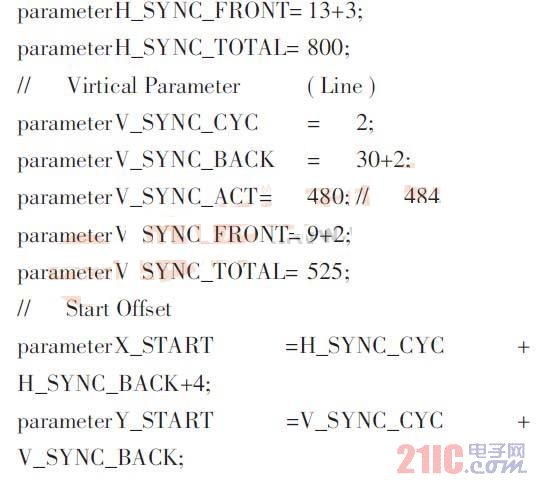

3 參數設置

本系統采用640×480 像素顯示, 刷新率為60Hz模式, 像素時鐘為25MHz。在VGA水平時序中, 每行包括800像素點, 其中640為有效顯示脈沖, 160為行消隱區; 而在VGA垂直時序中, 每場525行, 其中480有效, 45行為場消隱。其具體參數如下:

4 結束語

本文介紹的圖像采集和顯示模塊設計簡單,成本較低。由于其用高效硬件描述語言構成, 故其處理效率高, 具有很好的實用特性。