摘要:提出了一種基于FPGA 的數字幅頻均衡功率放大器的設計方案。系統在完成基于AD620前級小信號放大電路設計的基礎上,分析了阻帶網絡的幅頻特性;結合分析結果與FIR 濾波算法給出了相應的濾波器組成方案。后級功率放大電路采用分立MOS 管實現。

在現代通信系統中,碼間干擾是制約通信質量的重要因素。為了減小碼間干擾,需要對信道進行適當的補償,以減小誤碼率,提高通信質量,接收機中能夠補償或減小接收信號碼間干擾的補償器稱為均衡器。。本文提出了一種基于FPGA 的數字幅頻均衡功率放大器的解決方案。

1 系統總體設計

本文設計了一種數字信號幅頻均衡功率放大器的實現方案。設計主要由四個模塊組成。分別為小信號放大,帶阻網絡衰減,數字信號幅度的均衡處理以及功率放大。其中小信號放大部分由精密度高、噪音系數小的運算放大器AD620 實現;數字信號處理部分以FPGA 為處理核心,輔助以A/D、D/A 模塊進行模擬信號和數字信號的轉換;末級功放電路采用分立的MOS管來實現。

2 硬件電路設計

2.1 前置放大電路設計

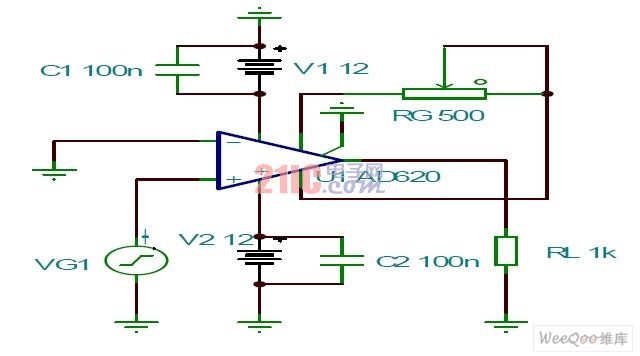

前置小信號放大器利用低功耗高精度的儀表運放AD620[3],在運放1 管腳和8 管腳之間介入可變電阻來實現增益可控,以滿足題目中要求放大倍數不小于400 倍。前級放大電路如圖1所示。根據AD620 的內部結構,其增益表達式如下:

Au=(R1+R2)/RG+1=49.4k Ω / RG+1,其中,RG 的單位為k Ω 。

圖1 AD620 放大電路

2.2 帶阻網絡的計算

阻帶網絡電路(詳見賽題)。根據基爾霍夫定律:

I1=I2+I3 (1)

U1= I1Z1+I3Z3 (2)

I3Z3= I2Z2+ U2 (3)

U2= I2RL=600*I2 (4)

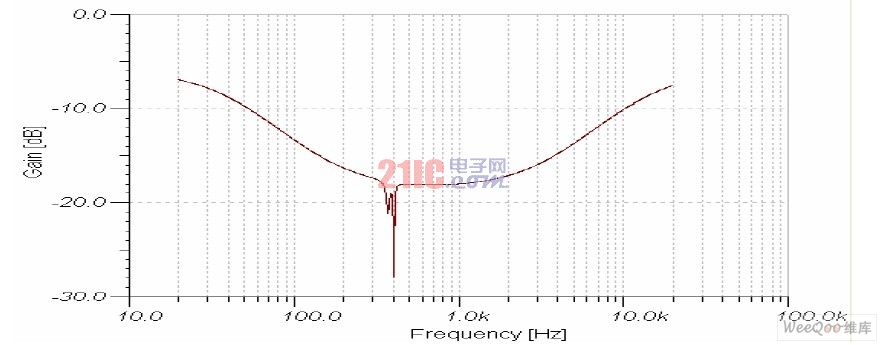

由式(1)(2)(3)(4)得U1 、U2 的關系:

(其中,Z1、 Z2 、Z3 分別為各諧振網絡的總阻抗)

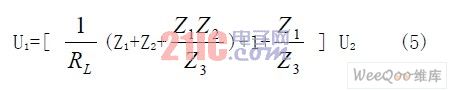

采用Tina 仿真軟件中的Signal Analyzer 測得帶阻網絡輸出信號的幅頻特性如圖2 所示。

圖2 帶阻網絡輸出信號的幅頻特性

2.3 數字信號均衡處理模塊電路設計

均衡技術的實質是在某種優化規則下完成隨機信號的最優濾波。因此信號的幅頻均衡問題即轉變為濾波器的設計問題。在大多數使用均衡器的通信系統中,信道特性是未知的;并且在許多情況下,信道響應是時變的,在這種情況下,應將均衡器設計成對信道響應是可調的;對時變信道,應設計成對信道響應的時變是自適應的。所以自適應均衡器在通信系統中得到普遍應用。但本賽題中,因為其采用帶阻網絡模擬實際的信道,但帶阻網絡中所有器件參數均為固定值,不存在時變問題,故設計的濾波器系數無需自適應。

均衡模塊采用Altera 公司的CycloneII 系列FPGA 作為信號濾波處理的核心; A/D 轉換模塊采用TI 的高速8 位A/D 轉換器TLC5540,它的最高轉換速率可達每秒40 兆字節;D/A 模塊采用10 位高速轉換芯片THS5651。

為實現對如圖2 所示的衰減進行補償,均衡模塊采用了截止頻率均為400HZ 的低通濾波器和高通濾波器的疊加。濾波器組原理圖如圖3 所示。

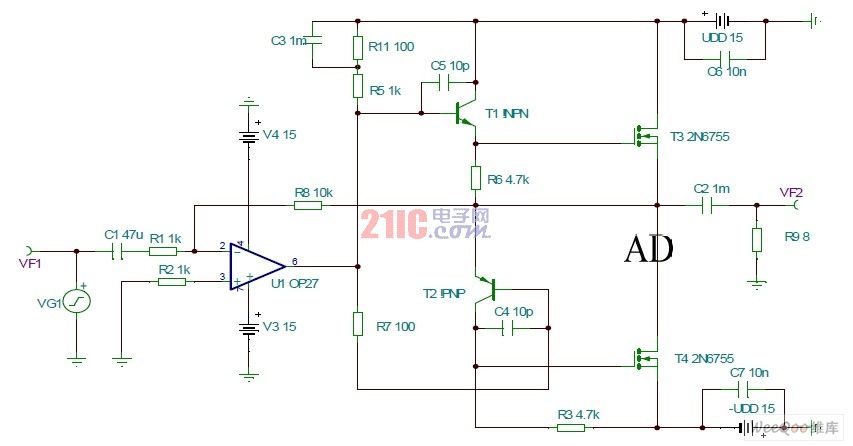

2.4 功率放大電路設計

根據題目要求,末級功率放大電路采用分立的大功率MOS 管實現,與分立的OCL 低功放相比,MOS 管功放具有激勵功率小,輸出功率大,輸出漏極電流具有負溫度系數,安全可靠,且有工作頻率高,偏置簡單等優點。電路如圖3所示,以運放的輸出作為OCL 的輸入,達到抑制零點漂移的效果。此方案中用三極管來驅動MOS 管,集基極間的電容C4、C5 為高頻防振電容。(注:圖中數據為參考數值)

圖3 MOS 管功率放大器

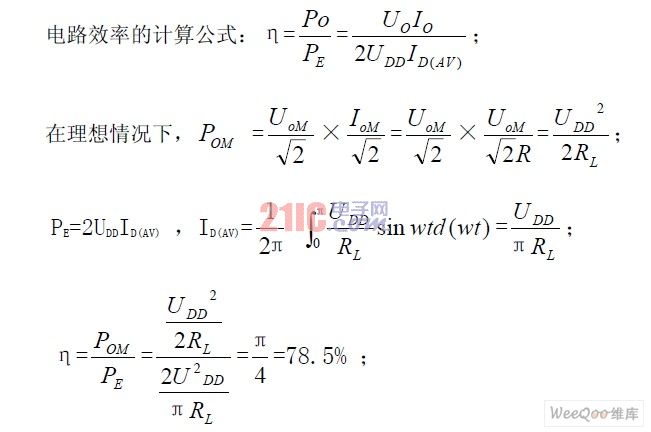

實際功率低于這個值,通過測量來計算出電路的效率。

3 軟件設計

Altera 提供了基于Matlab、DSP Builder 的數字濾波器設計方法。使用DSP Builder可以方便地在圖形化環境中設計FIR 濾波器,而且濾波器系數可以通過Matlab 的濾波器設計工具FDATool 計算完成。本文中采用直接I 型來實現該FIR 濾波器。首先設計一個系數可變的4 階FIR 濾波器節。然后再通過不斷的調用FIR 濾波器節,級聯起來,從而完成高階濾波器設計。

4 實驗結果與結論

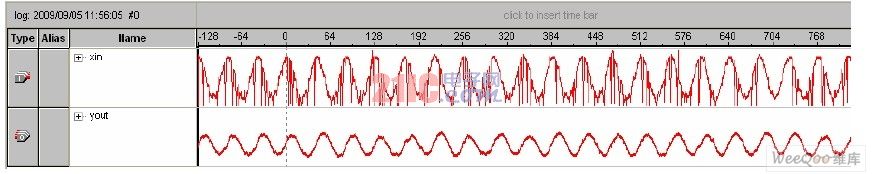

圖4 singaltap 測試結果

圖 4 為采用嵌入式邏輯分析儀SingalTap 得到的測試結果。其中,XIN 為由A/D 采樣得到的輸入信號,YOUT 為經過均衡程序處理過的輸出信號。從輸出YOUT 可明顯觀測到程序對輸入信號作出了補償,去除了噪聲,穩定了波形,起到了均衡信號的作用。本設計充分利用 FPGA 在數字信號處理上的優勢,在數字幅度均衡模塊中以FPGA 為平臺,實現數字信號幅度均衡的高速處理。同時本設計中前級放大電路不僅可以滿足賽題中的各項指標,還可以實現增益的可選擇性,可以在其他小信號放大的場合中運用。