摘 要: 介紹了一種基于新型FPGA的高速數(shù)字下變頻" title="數(shù)字下變頻">數(shù)字下變頻的實(shí)現(xiàn)方法,它充分利用數(shù)字下變頻的優(yōu)化算法以及FPGA領(lǐng)域的新技術(shù),去除由于數(shù)據(jù)速率過高而造成的各種瓶頸,極大地減少了計(jì)算量和FPGA片內(nèi)資源的消耗。

關(guān)鍵詞: 數(shù)字下變頻 多相" title="多相">多相濾波器 FPGA

在現(xiàn)階段的軟件無線電平臺(tái)中,直接對(duì)射頻(RF)進(jìn)行采樣還很難實(shí)現(xiàn),成本上也很不合算。所以在目前的研究中,大部分都是首先將射頻信號(hào)轉(zhuǎn)換到中頻(IF)上,在中頻對(duì)模擬信號(hào)進(jìn)行數(shù)字化,然后采用數(shù)字下變頻(Digital Down Conversion,DDC) 技術(shù),將采樣率較低的信號(hào)送給后續(xù)的基帶信號(hào)處理單元。

實(shí)現(xiàn)DDC主要有三種途徑:(1)采用已有的專用芯片;(2)自己制作專用芯片;(3)基于FPGA或DSP等通用芯片自建平臺(tái)實(shí)現(xiàn)DDC。但是在高采樣速率的系統(tǒng)中,如A/D" title="A/D">A/D采樣的速率為400MHz時(shí),這三種方法顯示出各自的弊端:商用專用芯片要求A/D轉(zhuǎn)換器轉(zhuǎn)換出的數(shù)據(jù)速率較低,比如AD6620要求數(shù)據(jù)速率小于70MHz,HSP50016要求數(shù)據(jù)速率小于75MHz;而自己制作專用芯片,由于成本過高和國內(nèi)技術(shù)條件的限制,在小規(guī)模的研發(fā)生產(chǎn)中幾乎是不可能的;用DSP芯片自建平臺(tái)實(shí)現(xiàn)DDC時(shí),雖然DSP可以高速執(zhí)行乘加指令,但由于DSP是串行執(zhí)行指令的,在高速處理中會(huì)遇到處理能力過低的問題;雖然用FPGA片內(nèi)資源可以同時(shí)進(jìn)行多個(gè)乘加運(yùn)算,但是用FPGA片內(nèi)資源實(shí)現(xiàn)的乘法器" title="乘法器">乘法器速度較慢,很難實(shí)現(xiàn)高速數(shù)據(jù)流的實(shí)時(shí)乘加處理。

本文介紹一種基于新型FPGA的高速數(shù)字下變頻的實(shí)現(xiàn)方法,它充分利用數(shù)字下變頻的優(yōu)化算法以及FPGA領(lǐng)域的新技術(shù),去除由于數(shù)據(jù)速率過高而造成的各種瓶頸,極大地減少了計(jì)算量和FPGA片內(nèi)資源的消耗。

1 數(shù)字下變頻算法的改進(jìn)優(yōu)化

數(shù)字下變頻的基本功能是將速率較高的數(shù)字中頻信號(hào)下變頻為數(shù)字基帶信號(hào),并降低信號(hào)的采樣速率。圖1是數(shù)字下變頻的基本模型。圖中將高速A/D轉(zhuǎn)換器的輸出信號(hào)送入數(shù)字下變頻器;經(jīng)兩個(gè)相乘器所構(gòu)成的混頻器后,將輸入的數(shù)字信號(hào)和復(fù)正弦信號(hào)產(chǎn)生器產(chǎn)生的正交正弦信號(hào)相乘,相乘結(jié)果為I、Q兩路信號(hào);再分別經(jīng)高抽取濾波器" title="抽取濾波器">抽取濾波器和有限長沖擊響應(yīng)(FIR)濾波器進(jìn)行處理。由這兩個(gè)濾波器構(gòu)成的復(fù)合濾波器的功能是低通濾波和抽取,其輸出是數(shù)據(jù)流降低了的數(shù)字基帶信號(hào)。

用FPGA實(shí)現(xiàn)圖1所示的經(jīng)典的數(shù)字下變頻會(huì)遇到如下幾個(gè)瓶頸:(1)當(dāng)中頻信號(hào)采樣速率較高時(shí)(大于200MHz),

FPGA無法用普通I/O引腳接收;(2)用常用的查表法無法實(shí)現(xiàn)高速NCO;(3)混頻器用到的高速乘法器無法實(shí)現(xiàn);(4)抽取濾波器中的高速乘法器和加法器實(shí)現(xiàn)困難。

解決上述問題的基本思想方法為:利用多速率信號(hào)處理理論,先抽取后處理,這樣就能避開由于高速率而帶來的瓶頸。

1.1 多相抽取濾波器

如果用傳統(tǒng)的方法對(duì)信號(hào)進(jìn)行抽取(抽取因子為D),其過程為:先將信號(hào)輸入一個(gè)L階的線性時(shí)不變FIR濾波器進(jìn)行抗混迭濾波,然后再進(jìn)行抽取;如果采用多相抽取濾波器,可以實(shí)現(xiàn)先抽取后濾波,其過程為:先對(duì)信號(hào)進(jìn)行抽取和分路,然后將抽取的結(jié)果輸入各多相分支濾波器。

多相分支濾波器的實(shí)現(xiàn)方法如下:把這個(gè)L階的抗混迭濾波器“拆分”為D個(gè)P階的濾波器,其中P=L/D是各個(gè)分支濾波器的階數(shù)。設(shè)原L階濾波器的沖擊相應(yīng)為H(n),n=0、1、2、…、L-1,那么每個(gè)分支濾波器的沖擊響應(yīng)由下式?jīng)Q定:

Hk(n)=H(k+nD)

式中,k表示第k支路,k=0、1、2、…、D-1;n=0、1、2、…、P-1。

利用多相分解得到的多相抽取濾波器如圖2所示,圖3是一個(gè)具體的多相濾波器的例子。在圖3中,濾波器要實(shí)現(xiàn)間隔為4的抽取,抽取濾波器的階數(shù)為16,經(jīng)多相拆分為4個(gè)分支濾波器。

1.2 高速NCO的等效處理

在數(shù)字下變頻的實(shí)現(xiàn)中,高速NCO的實(shí)現(xiàn)是系統(tǒng)的另外一個(gè)瓶頸。下面介紹高速NCO的等效處理。

將0~fs的頻帶作如下劃分:將整個(gè)頻帶劃分為N個(gè)信道,N=2D,D為抽取因子,設(shè)每個(gè)信道的帶寬為B,B=fs/D,相鄰信道間的交疊為50%。當(dāng)D=4時(shí),信道的劃分如圖4所示。只要抽樣速率符合奈奎斯特定理,這樣劃分就可以保證信號(hào)完整地存在于某一個(gè)信道內(nèi)。

假設(shè)帶通信號(hào)的調(diào)諧頻率為f0,將這個(gè)調(diào)諧頻率f0分解如下:f0=m![]() +fd,其中m

+fd,其中m![]() 是第m個(gè)信道的中心頻率,fd是f0和m

是第m個(gè)信道的中心頻率,fd是f0和m![]() 的頻差,取m的值使得fd最小。當(dāng)信號(hào)帶寬完全位于第m個(gè)信道中時(shí),由于第m信道的中心頻率為m

的頻差,取m的值使得fd最小。當(dāng)信號(hào)帶寬完全位于第m個(gè)信道中時(shí),由于第m信道的中心頻率為m![]() ,選擇序列

,選擇序列![]() 與輸入序列相乘進(jìn)行混頻,然后進(jìn)行抽取、多相濾波。這個(gè)過程如圖5所示,混頻之后的信號(hào)會(huì)帶有頻差fd,因fd較小,故可以在數(shù)字下變頻之后用其它的方法進(jìn)行消除。由于fd的消除并不是本文討論的主要問題,故下面只討論各個(gè)信道的下變頻。

與輸入序列相乘進(jìn)行混頻,然后進(jìn)行抽取、多相濾波。這個(gè)過程如圖5所示,混頻之后的信號(hào)會(huì)帶有頻差fd,因fd較小,故可以在數(shù)字下變頻之后用其它的方法進(jìn)行消除。由于fd的消除并不是本文討論的主要問題,故下面只討論各個(gè)信道的下變頻。

注意到Wm(n)具有以下性質(zhì):

當(dāng)n<D時(shí),

因此,如果信號(hào)帶寬位于偶數(shù)信道內(nèi),即m為偶數(shù),混頻器序列的周期為D,那么在多相濾波器中,Wm(n)可以相應(yīng)地分配給各個(gè)分支,其實(shí)現(xiàn)過程如圖6所示。

如果信號(hào)帶寬位于奇數(shù)信道內(nèi),即m為奇數(shù),混頻器序列周期為2D,且Wm(n)=-Wm(n+D),那么由于輸入數(shù)據(jù)在輸入多相濾波器之前已經(jīng)進(jìn)行過間隔為D的抽取,因此可以將抽取后的數(shù)據(jù)進(jìn)行模2編號(hào),編號(hào)為0的數(shù)據(jù)不變,編號(hào)為1的數(shù)據(jù)取相反數(shù)。其具體實(shí)現(xiàn)框圖如圖7所示。

圖7中只畫出了一路分支濾波器的實(shí)現(xiàn)方法,其它分支濾波器的處理同理可得。

2 高速數(shù)字下變頻的實(shí)現(xiàn)方案

綜上所述,通過對(duì)DDC實(shí)現(xiàn)方法的優(yōu)化,極大地減小了計(jì)算量,降低了對(duì)器件處理速度的要求,但是當(dāng)信號(hào)帶寬較寬時(shí),改進(jìn)算法后計(jì)算量仍然很大。比如,前端A/D轉(zhuǎn)換器輸出的數(shù)字信號(hào)速率為400MHz,經(jīng)過抽取因子為4的抽取后,信號(hào)的速率仍然有100MHz。顯然,用單片DSP很難完成抽取濾波和混頻處理工作,于是用FPGA實(shí)現(xiàn)DDC就成了唯一選擇。

運(yùn)用FPGA片內(nèi)的高速數(shù)據(jù)接口和DSP功能,結(jié)合上述優(yōu)化算法,就可以有效地解決高速數(shù)據(jù)實(shí)時(shí)處理的問題。

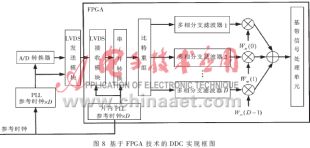

基于FPGA技術(shù)的DDC實(shí)現(xiàn)框圖如圖8所示。圖中,系統(tǒng)參考時(shí)鐘fr=fs/D。在A/D端,用PLL產(chǎn)生采樣時(shí)鐘fs,其上升沿和參考時(shí)鐘fr的上升沿對(duì)齊。在數(shù)據(jù)接收端,F(xiàn)PGA內(nèi)置PLL產(chǎn)生時(shí)鐘信號(hào)驅(qū)動(dòng)片內(nèi)LVDS接口,這個(gè)時(shí)鐘信號(hào)的上升沿和參考時(shí)鐘上升沿對(duì)齊。LVDS接口接收高速差分信號(hào),同時(shí)進(jìn)行串/并轉(zhuǎn)換和比特重組。串/并轉(zhuǎn)換過程等效地完成了抽取工作。

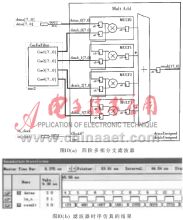

圖9(a)所示的是在Quartus II集成開發(fā)環(huán)境中調(diào)用庫函數(shù)ALTLVDS實(shí)現(xiàn)的LVDS接收接口,其功能為:接收速率為400MHz的輸入信號(hào),并作串/并轉(zhuǎn)換,以實(shí)現(xiàn)抽取因子為4的抽取,抽取后的數(shù)據(jù)分四路輸出,速率為100MHz。圖9(b)是LVDS接口的仿真波形,圖中rx_in[7..0]是A/D轉(zhuǎn)換器輸出的數(shù)字信號(hào),位寬為8位;rx_clock為參考時(shí)鐘fr,頻率為100MHz;rx_outclock是輸出信號(hào)時(shí)鐘,其頻率為fr,這個(gè)時(shí)鐘和輸出的數(shù)據(jù)之間有固定的相位關(guān)系,這個(gè)相位關(guān)系由數(shù)據(jù)對(duì)齊方式(一般是沿對(duì)齊)指定;rx_out[31..0]為串/并轉(zhuǎn)換后的輸出結(jié)果,經(jīng)過比特重組后,可以得到四路數(shù)字信號(hào)out1st[7..0]、out2nd[7..0]、out3nd[7..0]、out_4th[7..0],這四路信號(hào)將分別輸入四個(gè)分支濾波器。

抽取工作完成后,將各個(gè)支路的數(shù)據(jù)分別按時(shí)序送入相應(yīng)的分支濾波器。由于FPGA的邏輯資源和寄存器資源有限,而乘法器的實(shí)現(xiàn)(尤其是位數(shù)較高時(shí))比較多地耗費(fèi)FPGA內(nèi)部的寄存器資源,同時(shí)用邏輯和寄存器資源實(shí)現(xiàn)的乘法器運(yùn)算速度比較慢,常常達(dá)不到建立時(shí)間和保持時(shí)間的要求,因此應(yīng)該盡量利用片內(nèi)專用乘法器來實(shí)現(xiàn)濾波器。

在Quartus II中,用戶可以通過調(diào)用庫函數(shù)ALTMULT_ADD來使用片內(nèi)專用乘法器。圖10(a)中所示的是調(diào)用ALTMULT_ADD函數(shù)生成的四階多相分支濾波器。圖中dataa[7..0]為分支濾波器的輸入數(shù)據(jù);datab_0[7..0]、datab_1[7..0]、datab_2[7..0]、datab_3[7..0]是濾波器系數(shù)。in_clock為輸入數(shù)據(jù)的時(shí)鐘信號(hào),其頻率為fr,同時(shí)這個(gè)時(shí)鐘還控制著濾波器輸出的Pipeline時(shí)序,result[17..0]為濾波器的輸出數(shù)據(jù)。

圖10(b)是時(shí)序仿真的結(jié)果,由于運(yùn)用了片內(nèi)硬件乘法器,運(yùn)算速度大為提高。圖中in_clock的頻率為100MHz,在這個(gè)頻率下,濾波器輸出的數(shù)字信號(hào)完全可以達(dá)到建立時(shí)間和保持時(shí)間的要求。

用QuartusII實(shí)現(xiàn)DDC的頂層模塊如圖11所示。在實(shí)際系統(tǒng)中,它對(duì)如下中頻信號(hào)作DDC處理:中頻信號(hào)的調(diào)諧頻率為100MHz,信號(hào)帶寬為10MHz;前端A/D采樣速率為400MHz,位寬為8位;要求產(chǎn)生速率為100MHz的基帶信號(hào)。

由于信號(hào)帶寬位于第二信道內(nèi),因此混頻序列Wm![]() 。

。

在現(xiàn)有的技術(shù)條件下,用經(jīng)典的數(shù)字下變頻實(shí)現(xiàn)方案來對(duì)上述實(shí)驗(yàn)中的高速率信號(hào)進(jìn)行DDC處理幾乎是不可能的。而采用優(yōu)化過的算法同時(shí)結(jié)合FPGA領(lǐng)域的新技術(shù),不僅降低了系統(tǒng)對(duì)電子器件運(yùn)算速率的要求,而且使運(yùn)算量大約降低到原來的1/30,這樣就可以克服DDC處理中的各種瓶頸。本方案用于在FPGA片內(nèi)實(shí)現(xiàn)高速DDC,對(duì)于寬帶高中頻系統(tǒng)的數(shù)字下變頻處理有極大的參考價(jià)值。

上述DDC已運(yùn)用于某擴(kuò)頻通信設(shè)備中,效果良好,成功地實(shí)現(xiàn)了寬帶高速率信號(hào)的DDC處理。

參考文獻(xiàn)

1 Jerry Fudge, Mike Legako, C.Sehreiner.An Approach to Efficient Wideband Digital Downconversion[C]. Toronto,Canada:Proc ICSPAT, 1998:713~717

2 宗孔德. 多抽樣速率信號(hào)處理[M]. 北京: 清華大學(xué)出版社, 1996

3 李玉柏,彭啟琮. 軟件數(shù)字下變頻的實(shí)現(xiàn)與算法分析[J].通信學(xué)報(bào),2000;21(10):44~49

4 Altera Co. Implementing High-Performance DSP Functions in Stratix & Stratix GX Devices[EB/OL]. http://www.altera.com

5 Altera Co. Stratix Device Handbook[EB/OL].http://www.altera.com