傳統信號發生器大多由模擬電路構成,存在連線復雜、調試煩瑣且可靠性較差等缺點。以Verilog HDL編程語言和FPGA器件為核心的可調信號發生器的設計實現,提高了系統可靠性,實現了系統信號實時快速測量,也為其廣泛應用于實際領域創造了條件。

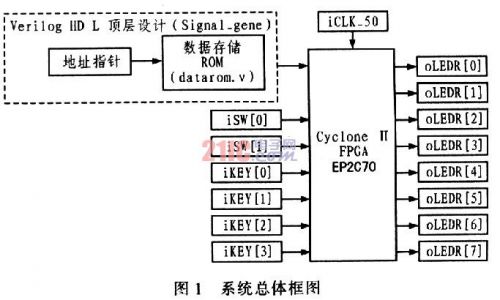

1 系統總體設計

可調信號發生器系統由頂層模塊、EP2C70器件、控制開關和輸入輸出模塊等部分組成,如圖l所示。在FPGA中實現的頂層文件包含地址指針和數據ROM2部分。其中,數據ROM由QuartusⅡ軟件中的LPM_ROM模塊構成,能達到最優設計,LPM_ROM由FPGA中的EAB或ESB實現。數據ROM中存儲正弦波、方波、三角波和鋸齒波4種信號各1個周期的波形數據(在此選擇1個周期128個數據樣點),地址指針讀取ROM中不同區域的數據,可產生不同的波形,并通過使用嵌入式邏輯分析儀SignalTapⅡ進行實時測試。根據讀取數據間隔的不同,即可實現調整頻率的功能。

2 系統功能模塊設計

可調信號發生器系統的功能模塊主要由頂層文件(Verilog HDL源程序)和波形數據ROM兩部分組成。波形數據ROM設計主要包括設計波形數據ROM初始化數據文件和定制ROM元件(datarom.v)。

2.1 頂層文件設計

本系統采用Ahera公司的CycloneⅡ系列EP2C70器件作為核心,通過QuartusⅡ軟件編寫Verilog HDL源程序,實現一個可以產生正弦波、方波、三角波和鋸齒波4種波形信號,并且能夠實現信號轉換及頻率可調功能的信號發生器。其中control控制產生波形的種類,00、0l、10、11分別產生正弦波、方波、三角波和鋸齒波;i控制讀取數據間隔,調整頻率。產生正弦波的源程序如下:

2.2 波形數據ROM初始化數據文件設計

初始化數據文件格式有2種:Memory Initialization FiIe(.mif)格式文件和Hexadecimal(Intel-Format)File(.hex)格式文件。本設計共需要產生4種波形,每種波形1個周期取128個數據,因此選用.mif格式文件初始化數據個數Number為512,數據寬度Word size取8位的ROM數據。在MATLAB中,調用wave=round(255*sin([0:2*pi/(2^9):2*pi])+256)’;函數,生成.mif文件,如圖2所示。

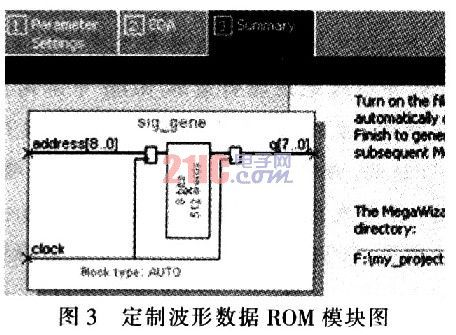

2.3 定制ROM元件

在QuartusⅡ中,利用Mega Wizard Plug-In Manager定制波形數據ROM,如圖3所示,經過LPM_ROM宏功能塊設定、選擇dmarom模塊數據線寬度和數據單元個數、選擇地址鎖存信號clock及數據文件完成LPM_ROM設計,產生可用于例化的波形數據ROM文件datarom.v。

3 軟件系統邏輯仿真

FPGA中的功能模塊進行綜合仿真后,生成配置文件。其系統邏輯功能仿真波形如圖4所示,各信號的邏輯功能和時序配合完全達到設計要求。

4 編譯下載

在將設計下載到DE2-70開發板進行驗證之前,首先要進行引腳鎖定,通過Assignments Editor依次對所有15個引腳進行鎖定,其中PIN_-AA23和PIN_AB26分別對應control[0]和control[l]DE2-70開發板上的SW0和SWl控制4種波形的選擇,具體引腳鎖定如圖5所示。

將編譯產生的下載文件(.sof)配置進FPGA中,通過選擇DE2-70開發板的JTAG方式和USB BlasterⅡ編程線進行編程下載,為使用嵌入式邏輯分析儀實時測試所設計的信號發生器做好準備。

5 綜合分析

SignalTapⅡ嵌入式邏輯分析儀提供了一種對器件進行實時測試的方法,它可以隨設計文件一起下載到目標芯片中,用以捕捉目標芯片中有關信號節點處的信息,而不影響芯片的正常工作。SignalTapⅡ將測試得到的信號暫存于目標器件的片內RAM中,再通過器件的JTAG端口和USBBlasterⅡ編程線將采得的信號傳出,以供計算機分析。

下載成功后,設定DE2-70開發板的工作模式和恰當的控制信號,使計數器正常工作(inclock頻率設為750kHz),啟動SignalTapⅡ進行測試,通過改變輸入控制信號得到如圖6所示的4種信號波形圖。改變i的取值,可看到信號頻率也會隨之變化。

6 結束語

本設計充分利用FPGA具有的靜態可重復編程和動態可系統重構的特性,使得硬件功能像軟件一樣通過編程修改,從而提高開發效率,縮短研發周期。測試結果表明:系統軟件模擬數據和理論定制波形相吻合,頻率調節方便,僅在波形光滑程度上存在很小誤差,但這不影響設計結果、波形的觀察和測量以及該可調信號發生器的使用。通過增加采樣點的數量及提高程序語句的精確與簡練度,可減少誤差影響。