引言

隨著網絡的迅速發展,對安全性的需要越發重要。然而,盡管網絡技術進步很快,安全性問題仍然相對落后,并且在很多情況下只能靠虛擬私人網VPN和防火墻。因虛擬私人網是構建在Internet外部結構上的,必須采取某些措施保證安全性問題。一種方法是使用因特網協議安全性(IPSec)標準。IPSec是一組協議,它在IP協議層提供安全保密的通信。IPSec協議有通道和傳輸兩種通信模式,為了保證在高速通信中的數據安全,在設計中使用硬件加速來實現IPSec中的加密和認證。IPSec中的加密部分使用三重DES算法,或使用RC5、IDEA、Blowfish和CAST-128等算法作為加密手段。在IPSec協議中認證使用SHA-1和MD5單向散列函數算法實現,通過使用FPGA高速實現SHA-1消息認證算法。

SHA-1算法介紹

安全散列算法SHA(Secure Hash Algorithm,SHA)是美國國家標準和技術局發布的國家標準FIPS PUB 180-1,一般稱為SHA-1。其對長度不超過264二進制位的消息產生160位的消息摘要輸出,步驟如下。

首先填充消息使其長度恰好為一個比512的倍數僅小64位的數。填充方法是附一個1在消息后面,后接所要求的多個0,然后在其后附上64位的消息長度(填充前),使消息長度恰好是512位的整數倍。

5個32位變量,用十六進制表示初始化。然后開始算法的主循環,一次處理512位消息,循環次數是消息中512位分組的數目。

先把這五個變量復制到另外的變量中,A到a,B到b,C到c,D到d,E到e。

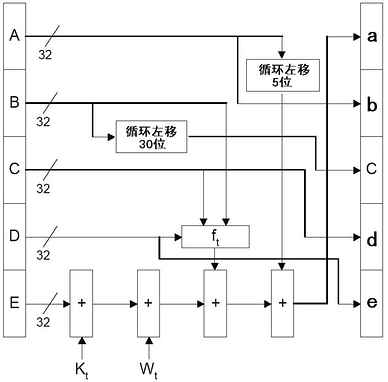

主循環有4輪,每輪20次操作,每次操作對a、b、c、d、e中的3個進行一次非線性運算,后進行移位和加運算,運算的過程見圖1。a、b、c、d和e分別加上A、B、C、D和E,然后用下一數據分組繼續運行算法。最后的輸出由A、B、C、D和E級聯而成。

SHA-1算法的FPGA實現

實現SHA-1算法時,用軟件先對消息進行預處理,使消息長度恰好是512位的整數倍,再以FPGA實現對消息摘要計算的加速。

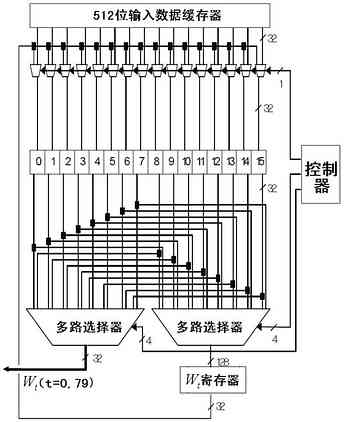

FPGA的編程一般用Verilog HDL或者VHDL進行,本設計采用了VHDL語言對SHA-1算法進行描述。SHA-1算法FPGA加速器實現分為兩大部分,分別是80個32位臨時值Wt(W0至W79)的生成,以及對32位臨時值Wt循環處理生成160位的消息摘要。圖2為將子分組Mj(0≤j≤15)變成80個32位Wt(Kt至W79)的電路框圖,在設計時,用512位寄存器和2個多路選擇器生成臨時值Wt(0≤t≤79)。

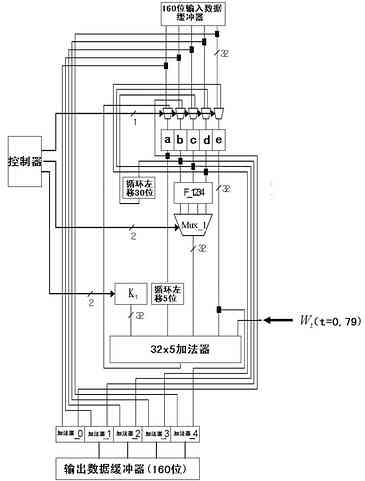

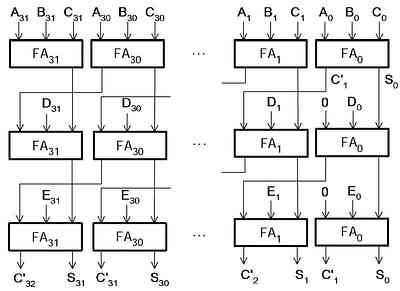

圖3中160位輸入數據緩沖器用來放置初始數據(5個32位變量A、B、C、D和E),而F1234代表SHA-1算法中的4組非線性函數ft(X,Y,Z),根據需要用多路選擇器Mux-1選擇其中一個(ft(X,Y,Z)=(X∧Y)∨((X)∧Z),對于t=0至19;ft(X,Y,Z)=X臲臵,對于t=20至39;ft(X,Y,Z)=(X∧Y)∨(X∧Z)∨(Y∧Z),對于t=40至59;ft(X,Y,Z)=X臲臵,對于t=60至79),4個常數為Kt存在ROM中(即組件),32×5加法器將5個32位數相加,為加快相加的計算速度使用先行進位加法器來執行,具體連接結構見圖4。

采用Aldec公司的Active HDL V5.1對SHA-1算法進行功能模擬,測試值和中間結果使用Crypto++中的庫函數的輸入值和運算結果,并使用這些測試值和中間結果對SHA-1算法的VHDL語言描述進行驗證和查錯,經驗證的SHA-1算法的VHDL語言描述使用Xilinx公司的ISE 4.1進行邏輯綜合、映射、布局和布線,生成網表用于時序仿真,最后將bitstream文件下載FPGA器件上,完成設計開發。

FPGA的外圍電路和控制軟件

將SHA-1算法的FPGA實現做在PCI卡(安全性算法協處理器)上,實現協議中的安全性算法。在安全性算法協處理器中,FPGA執行加密解密操作,PIC控制器(用Zenic公司的 ZEN7201AF)作為PIC總線與協處理器的接口,SRAM存置FPGA的配置數據,配置控制器 (用Xilinx公司的XC95108-7實現)輸出地址和數據信號對FPGA進行配置,用Realtek公司的網絡控制器RTL8019AS實現PCI卡與網絡連接,協處理器的結構見圖5。而FPGA的配置數據(加密算法的FPGA高速實現)放在硬盤上,通過操作系統BSD Unix 4.4中的PCI卡設備驅動程序,經由PCI總線下載到安全性算法協處理器的SRAM中,后用各種加密算法的配置數據對FPGA進行配置,實現真正“現場可編程”,各種加密解密算法都可以通過FPGA的內部配置用硬件結構實現了。

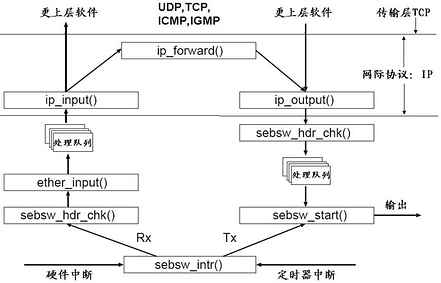

在軟件控制方面,安全性算法協處理器驅動程序是通過函數Sebsw_intr()直接控制協處理器,此函數有來自網絡控制器的中斷和來自操作系統內核的時鐘中斷兩個輸入;Sebsw_hdr_chk()檢驗消息包的頭部,如果發生硬件中斷,Sebsw_intr()調用Sebsw_hdr_chk()函數;函數ether_input()檢查接收到的數據類型,將接收到的分組加入到隊列處理;函數ipinput()決定分組的最終地址,如果最終地址為本地地址,函數將分組傳給更上一層軟件,如果最終地址為非本地地址,則將分組傳給ip_forward();函數ip_output()從收到的數據中生成IP數據包,然后Sebsw_start()將數據包傳給網絡控制器。軟件控制結構見圖6。

結束語

實驗結果表明,在FPGA的頻率為31.42MHz時,數據處理速度為214Mb/s,完全滿足設計要求。本設計是課題“因特網協議安全性(IPSec)標準FPGA高速實現”的一部分,設計中還將包括三重DES算法、IDEA算法、高級加密標準AES等。