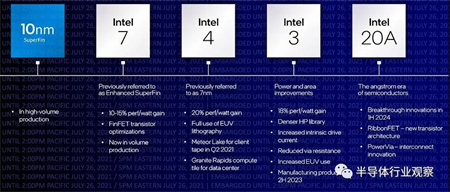

英特爾在 7 月下旬的英特爾加速活動期間宣布其面向未來的半導體工藝節點的新名稱時受到了很多抨擊。按照英特爾的說法,他們的新節點稱為 Intel 7、4、3 和 20A。但業內權威人士抨擊該公司將 10 納米增強型 SuperFin 工藝節點命名為“Intel 7”的做法(英特爾上周在其英特爾創新開發者大會上宣布并展示了使用Intel 7 工藝節點構建的第 12 代 i5、i7 和 i9 酷睿處理器,因此該工藝技術顯然掌握得很好)。該公司現在把“Intel 4” 用于之前稱為 7nm 的節點。Intel 3 和 Intel 20A 是全新的節點名稱。

在筆者看來此次節點重命名一部分源于營銷,另一部分只是面對現實。

英特爾已重新命名其即將推出的工藝節點,以符合行業慣例而不是其自身對現實的看法

過去,英特爾曾表示其 10nm 增強型 SuperFin 節點(現更名為Intel 7)在功率和性能上與臺積電的 7nm 節點大致相當。這很令人困惑,不是嗎?該公司還表示,行業分析師已要求英特爾更新其工藝節點命名法,以反映該公司在半導體工藝領域的真實競爭地位。所有這些都是重命名節點的營銷部分。

而現實是這樣的:納米命名法在很長很長一段時間內都不準確。不適用于英特爾,當然也不適用于任何其他硅代工廠。這種情況就像熱門喜劇電視節目“這到底是誰的臺詞?”中的評分系統,分數不重要。

多年前,工藝節點命名是基于晶體管的最小特征尺寸。該命名約定是專門為平面 MOS 晶體管開發的,最小晶體管特征總是晶體管的柵極長度。當 FinFET 取代平面 MOS 晶體管時,這種命名約定就消失了,所有供應商的工藝節點名稱都變成了您從等效平面 MOS 晶體管獲得的功率和速度的估計等效值。除了他們實際上無法再制造那些平面 MOS 晶體管。平面晶體管技術放棄了。MOS 晶體管在目前的光刻水平上不能很好地工作。這就是我們轉向 FinFET 的原因。早在 2011 年,英特爾就在 22 納米節點上推出了其首個 FinFET 工藝。

RibbonFET 和埃

十年后,晶體管的基本結構即將再次發生變化。

FinFET 柵極從三個側面驅動。這比平面 MOS 晶體管中驅動的多了兩個側面,它以更復雜的制造技術為代價帶來更好的晶體管性能。然而,驅動 FinFET 晶體管柵極的三個側面不再達到所需的速度和漏電流。我們現在必須驅動柵極的所有四個側面。這些 4 邊柵極驅動結構通常稱為“Gate all around”或 GAA。

英特爾稱其 GAA 晶體管為“RibbonFET”,目前他們計劃在Intel 20A 工藝中推出改技術,該工藝將于 2024 年上半年出現(除非出現延遲)。注意進程名稱中的“A”。“A”代表“埃”。英特爾沒有像以前的工藝節點那樣稱這個工藝節點為“intel 2”,而是將單位從納米切換到埃。一埃是 10 -10 m,或十分之一納米。我認為我們應該簡單地忽略英特爾從更大的工藝節點中刪除了“nm”這一事實。

據推測,這種對埃的命名更改允許分數納米節點命名。這與我們之前使用的單位微米的情況類似。回到黑暗時代,我們有 3、2.5、2、1.5、1.3、1.2 和 1 微米的工藝步驟,然后是 0.8、0.75、0.7、0.5,一直到 0.25 微米左右。在那個點附近的某個地方,我們從微米跳到了納米。根據我的記憶,命名法的變化發生在 0.18 微米處,通常稱為 180 納米。那是什么時候?大約 1998 年,這發生在二十多年前。

這意味著在納米工藝節點尺將被使用近四分之一個世紀以后,埃時代正式到來。Intel Angstrom 命名法允許公司擁有名為 Intel 18A、Intel 17A、Intel 16A 等的工藝節點。這聽起來比 Intel 1.8、Intel 1.7、Intel 1.6 等等好多了,不是嗎?看起來他們也能通過這種方式取得了更大的進步,對嗎?

然而,我們必須承認,從一個節點到下一個節點的進度不像以前那么大了。從上圖中,您可以看到從一個英特爾工藝節點到下一個節點的性能/瓦特提高了 10% 到 20%,并且該圖像甚至沒有討論密度改進。

摩爾定律在墳墓中腐爛了

基于以上所有內容,我有一個非常悲傷的消息要告訴你,摩爾定律已經死了。即使英特爾首席執行官帕特·蓋辛格 (Pat Gelsinger) 上周在英特爾創新活動期間做出了在未來 10 年內每年都滿足或擊敗摩爾定律的大膽而熱情的承諾。然而通過從一代到下一代削減幾埃來擴展工藝節點并不能實現晶體管密度的兩倍,而這正是摩爾定律的真正本質。

從我的角度來看,圍繞摩爾定律存在很多困惑。

首先,摩爾定律長期以來一直與 Dennard Scaling 緊密交織和混淆,Dennard Scaling 表示平面 MOSFET 的速度和功率隨著晶體管密度的增加而按比例降低。在半導體的早期,當一種新的工藝技術將晶體管面積縮小 50% 時,晶體管的速度會增加一倍,而功率則會減半。每隔幾年,我們就獲得了一半大小的晶體管,其速度是每個新工藝節點的一半,而運行速度則是一半。那時確實是非常好的時代,摩爾定律正在全面發揮作用。然而,Dennard Scaling 是一個專門針對平面 MOS 晶體管的觀察結果,我們已經有十年沒有使用最先進的新工藝節點制造這種晶體管了。

摩爾定律不涉及晶體管功率或速度。摩爾定律說,芯片上的晶體管數量大約每兩年翻一番。這就是它所說的。喜歡的可以查一下。Gordon Moore 于 1965 年 4 月 19 日在《電子》雜志上發表的原始文章,文章標題是“將更多元件塞進集成電路上”。它方便地發布在英特爾的網站上供您閱讀。這篇文章發表于摩爾和鮑勃諾伊斯創立英特爾的三年前,當時摩爾和諾伊斯都還在飛兆半導體工作。

摩爾在他開創性的文章中進行了令人難以置信的預測壯舉。半導體行業最終接受了他的預測并將其轉化為基于極少數數據點的自我實現預言。第一個數據點是單個晶體管。第二個數據點是最早的商用集成電路之一,稱為 Fairchild μLogic Type G RTL 芯片的 3 輸入 NOR 門。

根據大衛帕特森博士的說法,摩爾定律一直持續到 2015 年,因為它耗盡了氣力。帕特森怎么會說摩爾定律在 2015 年消亡,而英特爾的高管們一致讓您相信摩爾定律在今天仍然存在并且很好?這是因為摩爾 1965 年論文第 2 頁上的一句話。那句話是:“……在單個半導體襯底上生產越來越大的電路功能。” (重點是我的。)摩爾定律是關于單片集成電路的,而這不是半導體行業現在的發展方向。

事實上,在2003年舉辦的第50屆國際固態電路會議上,在一個題為“No Exponential is Forever”的議題中,戈登·摩爾本人斷然指出:“沒有任何的物理事物可以持續成倍改變。” 摩爾定律在將近 20 年前就已經消亡,而摩爾親眼目睹了這一點。

目前標志著摩爾定律終結的典型代表是英特爾自己的 Ponte Vecchio GPU。英特爾正在使用 47 個有源“tiles”(英特爾對多芯片封裝中的小芯片或芯片的名稱)組裝這種集成設備,由來自五個不同半導體工藝節點的多家半導體供應商制造,所有這些都使用 2.5D 和 3D 組裝組合在一個封裝中技術來生產具有超過 1000 億個晶體管的集成產品。

有人聲稱摩爾在他的文章中預見到了多芯片封裝。他們引用了這句話:

“事實證明,用較小的功能構建大型系統可能更經濟……”

但他們似乎省略了這句話的后半部分:

“……它們是分開封裝和互連的。”

在這里,摩爾清楚地討論了在一塊板上使用多個單獨封裝的芯片,這是自 1960 年代集成電路首次出現以來板級設計的主要內容。

在我看來,摩爾顯然不是在用這句話來預測今天的多芯片封裝。事實上,他的文章討論了在 10 年內(即 1975 年)出現每個 IC 具有 65,000 個元件的單片 IC 的可能性,這比 1965 年摩爾的文章出現時任何單個印刷電路板所能容納的分立元件都要多。

誰可能需要超過 65,000 個組件?如果摩爾當時考慮過,而且他可能確實考慮過,那么他一定已經看到,直到很遠很遠的將來才會需要多芯片封裝技術。嗯,那個未來已經到來。

英特爾的 Ponte Vecchio GPU 整合了來自五個不同工藝節點的 47 個tiles,將 1000 億個晶體管塞進一個封裝中。(圖片來源:英特爾)

多芯片封裝之所以有意義,只是因為不同的工藝節點提供不同的成本/性能/能力權衡,因為我們處于當前芯片制造設備的光罩極限,并且因為 2.5D 和 3D 封裝技術現在足夠實用和經濟這種方法在商業上有效。假設您擁有可靠且經濟地組裝所有這些tile或小芯片所需的制造工藝,為什么不應該使用最高效的半導體工藝節點制造模塊和子系統?Ponte Vecchio無疑是一個工程奇跡,但它絕對不是單片芯片,因此它不是原始摩爾定律實際應用的例子。

除了摩爾定律的大量神話基礎之外,對于我們大多數人來說,英特爾如何將 1000 億個晶體管塞進 Ponte Vecchio 封裝實際上并不重要。對于在設計中使用 Ponte Vecchio GPU 的系統工程師來說,這并不重要。對于使用在 Ponte Vecchio GPU 上運行的圖形軟件或計算機游戲的人來說,這并不重要。設備的性能、功率和價格(所有工程設計的三個基本“P”)對于我們這些不熟悉封裝的人來說非常重要。

英特爾計劃以類似的方式構建公司下一代至強處理器的代號 Sapphire Rapids。英特爾將使用基于公司 EMIB(嵌入式多芯片互連橋接)技術的 4 個 CPU 塊和 2.5D 組件制造 Sapphire Rapids。Sapphire Rapids 處理器的多個版本還將在同一封裝中集成多個 HBM2(高帶寬內存 2)DRAM 堆棧。

英特爾的 Sapphire Rapids 是下一代至強 CPU,將包含由四個 EMIB 橋連接的四個 CPU 塊。(圖片來源:英特爾)

多芯片封裝并非英特爾獨有。AMD、Nvidia 和 Xilinx 都生產集成芯片,這些芯片在外部看起來像單片集成電路,但在內部是多芯片設備——相互連接的tile或小芯片的集合。

例如,賽靈思在 2011 年推出了 Virtex-7 2000T FPGA。它基于多芯片封裝,將四個 FPGA 管芯放在一個硅中介層之上。臺積電為賽靈思制造該器件。大約在同一時間,多芯片封裝使賽靈思能夠在其 Virtex-7 580T FPGA 中集成 28 Gbps 收發器,然后才能將這些收發器直接構建到 CMOS FPGA 芯片中。賽靈思在每一代新 FPGA 中都擴大了多芯片封裝的使用范圍。這很好地表明多芯片封裝運作良好,至少對于 IC 市場的高端而言是這樣。

總而言之,歡迎來到埃時代。這是一個“超越摩爾”的時代。現在擺脫了將所有東西都放在一個芯片上的情感和經濟需求,這個半導體制造的新時代已經生產出比以往任何時候都更大、更好的集成設備。僅僅依靠單片 IC 和摩爾定律是無法提供這些好處的。

摩爾定律可能已死,但摩爾定律的精神永存。