快速傅里葉變換(FFT)算法實現的流水線結構FFT處理器在實時專用處理器中得到了廣泛應用.Bi和Jones提出一種固定1024點流水線FFT處理器結構,該結構在運算的每級只采用一個復數乘法器.基于此結構Hasan設計了一種能夠進行16,64,256和1024點FFT運算的可變點流水線FFT處理器,增強了處理器運用的靈活性.但該處理器結構所需的中間數據及旋轉因子存儲容量較大,各級的地址控制邏輯比較復雜,運算時間較長,不適于對速度和面積要求越來越高的應用場合.作者提出了一種實時可重配置的FFT處理器.該處理器采用小點數內部流水和大點數二維化處理結構,通過控制各處理模塊實現4,16,64,256和1 024點復數FFT運算,并給出了該結構與Hasan結構的性能比較.

1 可重配置FFT算法原理

N個樣本點的離散博里葉變換(DFT)表達式為

式(2)表明,計算組合數N=r1 r2點DFT等價于先求出r2組r1點的DFT,其結果乘以旋轉因子后,再計算r1組r2點的DFT.

基-4時間抽取FFT算法中,16點FFT運算可以分為兩級,第1級基本運算是4點序列的DFT.因此,如果只取16點FFT運算的第1級運算便可同時完成4點FFT運算.

2 可重配置FFT處理器的實現

2.1 系統設計

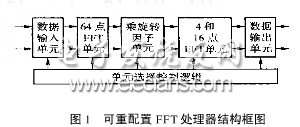

FFT處理器由數據輸入單元、固定64點FFT、流水處理單元、中間乘旋轉因子單元、4和16點FFT可變流水處理單元及數據輸出單元組成.如圖1所示.

在進行FFT運算時,單元選擇控制邏輯根據需要變換長度N激活相應的處理單元.

根據式(2)對1 024點輸入數據進行FFT運算,首先數據輸入單元要按照N=rlr2=64×16完成對輸入1 024點數據的分解,然后固定64點FFT流水處理單元完成16次64點運算.運算結果分別與1024個中間旋轉因子相乘,然后乘旋轉因子單元完成對這1 024個結果的整形,并使用4點和16點可變處理單元完成64次16點變換.數據輸出單元完成對結果進行最后整形并同時輸出1個塊浮點溢出檢測指數和1 024個數據結果.同理對于256點的FFT運算,數據輸入單元按照N=r1r2=64×4進行分解運算即可.

2.2 地址生成

可重配置FFT處理器包括輸入數據地址產生單元、64點數據旋轉因子地址產生單元、中間乘旋轉因子地址產生單元、中間數據存取地址產生單元、4,16點FFT數據及旋轉因子地址產生單元和輸出數據地址產生單元.每個單元都由計數器和地址變換器構成,每周期產生一組地址.由于采用的是Cooley-Tukey算法同址運算規則,倒序輸入正序輸出.因此針對不同長度的FFT運算,地址變換器只需要對計數器的輸出值進行不同的變形即可.

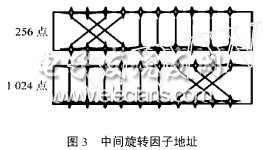

由于要實現的最大運算點數為1 024,同時采用流水乒乓存儲結構,因此輸入、中間、輸出單元的地址深度為2,則這3個地址產生器中的計數器為11位,最高位作為乒乓選擇控制位.產生的各個單元地址如圖2所示.中間數據地址產生單元只需要生成256點和1 024點數據地址即可.中間數據存地址即為輸入數據地址.輸出數據地址只需要產生4,16,256和1 024點數據地址.256個旋轉因子可從1 024個旋轉因子中抽取得到.產生的中間旋轉因子地址如圖3所示.4,16和64點FFT處理器采用Hansan結構,它們的存儲容量遠小于一個整1 024點所需的存儲容量.為了加快數據訪問時間,同時減少存儲器容量,16點FFT運算所需的旋轉因子值可以直接存儲為常數. FFT同時采用塊浮點定標方式,以提高運算精度.

3 ASIC驗證及性能分析

使用VHDL硬件編程語言在RTL級對可重配置FFT處理器進行了代碼描述.基于SMIC 0.18μm標準單元工藝庫,用Synopsys DesignCompiler綜合工具進行邏輯綜合,使用Astro 工具進行版圖規則及布局布線;用仿真工具VCS進行邏輯動態仿真,用參數提取工具Star-RCXT提取寄生參數并使用靜態時序分析工具PrimeTime對整個設計系統進行靜態時序分析.處理器的ASIC版圖如圖4所示存儲器按照圖1所示數據流的方向排放,以便于邏輯單元布局布線.處理器版圖采用了3層電源環結構.采用該結構一方面可增加管腳供電能力,另一方面也可有效減小芯片面積(處理器芯片面積為3.6mm×3.7mm).

表1為作者所提出的結構與Hason結構的性能比較.其中數據用36 bit表示(高18 bit為實部,低18 bit為虛部),指數用6bit表示,結果比較用kbit表示.由表1比較結果可知,作者所提出的可重配置FFT處理器結構不僅減小了45%的存儲器資源,而且節省了52%的處理時間.該處理器芯片在連續工作100 MHz時鐘頻率時,處理第1組1 024點FFT序列需要24.8 μs,以后每10.24μs給出1組1 024點運算結果.表2為FFT處理器進行各種點數運算的功耗.可重配置結構采用復用器及相關的邏輯電路實現門控時鐘電路,這樣,在進行不同點數運算時可以啟動不同的運算單元(屏蔽不需要的運算單元),以降低功耗.由表2可知,在啟動64點FFT運算模塊時,系統功耗較1 024點FFT運算量降低了約49%,而 4點運算量降低了約80%.

4 結論

提出一種可重配置FFT處理器的ASIC芯片設計與實現、該芯片采用子模塊基-4單元級聯流水線結構,使用雙口RAM進行乒乓存儲,不僅減少了硬件實現資源,而且提高了處理速度,具有連續計算4,16,64,256和1 024點復數輸入FFT的運算功能.結構設計采用模塊化設計,縮短了芯片設計開發周期.處理器芯片面積為3.6mm×3.7mm,適用于實時、高精度動態變換應用場合.