1 引言

由于電源適配器芯片中內嵌集成或需要外部連接功率LDMOS 管,應用中的LDMOS 管又需要直接和高壓相聯接并通過大電流(目前的LDMOS 管已經能耐受數百乃至近千伏的高壓)。因此,如何保障芯片和LDMOS 管的安全工作是芯片設計的重點之一。

利用片上二極管正向壓降的負溫度特性來監測芯片的熱狀態,進而控制功率LDMOS 管的開關是一種可行的安全設計方法。但是由于硅片存在熱惰性,故不能做到即時控制。該方法更適宜作安全設計的第二道防線。

從芯片設計看,要確保適配器芯片使用的安全性,比較好的方法應該是直接監測流經LDMOS 管的大電流或LDMOS 管的漏極電壓,以實時監控芯片的工作狀態。一般采取兩種方案:(一)在功率MOS 管源端對地串聯一個小電阻用于檢測源極電流,如圖1(a)所示;(二)是通過檢測電路監控LDMOS 的漏端電壓,如圖1(b)所示。前一種方案至少有以下缺點:(1)由于工藝存在離散性,電阻值很難做到精確(誤差在20%左右);(2)源極串入電阻后,使原本導通電阻很大的LDMOS 管的管壓降進一步增大,功率處理能力變弱;(3)電阻上流過大電流,消耗了不必要的能量,降低了開關電源的轉換效率。

圖1(a)串聯電阻檢測電流圖1(b)直接檢測漏端電壓

而采用后一種方案,因為利用了集成電路的特點(電壓采樣電路的電阻比精度很容易做到1%),電路處理并不太復雜。重要的是LDMOS 管沒有源極串聯電阻,可減少能量損耗,不影響LDMOS 管的功率處理能力,提高了電源轉換效率。

直接檢測漏端電壓判斷LDMOS 是否過流的設計思想是在LDMOS 管導通時,通過采樣電路檢測LDMOS 漏端電壓,經比較,過流比較器輸出一個低電平過流信號以關閉LDMOS 管;而在LDMOS 管截止期間,采樣電路不工作,同時為了提高可靠性將比較器窗口電平適度拉高。

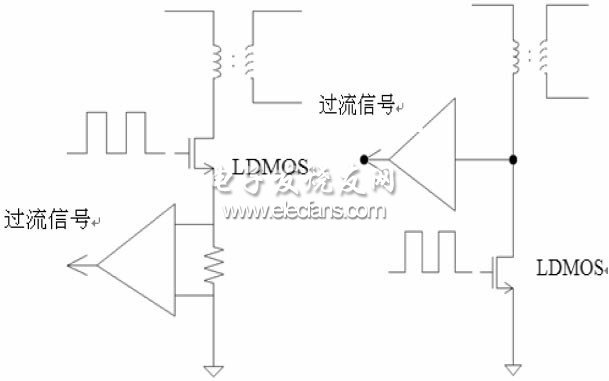

圖2 是實現上述功能的電路框架圖,由過流比較模塊、控制邏輯等組成。

圖2 過流保護電路框架

2 電路設計

2.1 過流比較模塊

過流比較模塊主要由前沿消隱Leadedge、采樣電路Sample、比較電壓產生器ToCompare 和過流比較器Comparator 等組成,如圖3 所示。

前沿消隱電路由于存在片上寄生或外接電容和電感的影響,在LDMOS 管開啟的瞬間,會在LDMOS 管漏極輸出端出現尖峰電壓,可能造成過流誤判。必須增設前沿消隱電路,即對LDMOS 管柵控電壓產生一個時間延遲,使在LDMOS 管開啟的瞬間將過流比較器閉鎖,等到尖峰通過后,再對LDMOS 管漏極信號進行采樣測量和過流判斷,從而消除漏電壓尖峰的影響。如圖3 所示,我們在其中加入一個偏置在固定電壓V(BIASN)的NMOS 管,它相當于一個固定電流源,以限制電容放電的時間。

圖3 過流比較模塊電路圖

合理設計相關的器件參數可以控制延遲時間的大小。

采樣電路用開關控制電路實現對LDMOS 漏端的周期性電壓采樣,其中分壓電路可采用大阻值有比電路結構。根據集成電路的特點,電阻比值的誤差很容易被控制在1%范圍之內。

當LDMOS 的柵電壓V (GATE) 為高,即LDMOS 管導通時,使圖3 中的采樣開關管M10(具有較高耐壓和較低導通電阻特性)也導通,同時開始采集LDMOS 管的飽和漏極電壓;而當LDMOS 管的柵電壓V(GATE)為低,即LDMOS 管關閉時(非過流現象),采樣電路則不工作。

比較電壓產生器的電路工作原理如下:由于過流狀態只發生在功率LDMOS 管柵極為高電平狀態。故當V(GATEDelayed)為低電平時,I1、I2和I3將同時對電容Ccompare充電, 使比較電壓V(Compare) 值升高。考慮到采樣電壓最大值為2.5V,為避免誤操作,可設置比較電壓值為2.7 V,以使后繼比較電路工作的門限電平增加,提高抗干擾能力;與此同時,采樣電容Csample將通過電阻R2快速放電,使采樣電壓V(Sample)快速變為零,即相應輸出為非過流狀態。

而當柵極電壓V(GATEDelayed)為高電平時,輸出比較電壓則變為V(Compare)=I1×R3=1.0 V。

過流比較器過流比較器采用常見的NPN 差分對管的輸入方式,恒流源偏置。與傳統恒流源偏置略有不同的是在偏置電路中增加了MOS 開關,當V(GATE)為高時(此時LDMOS 和該MOS 開關同時導通),電路圖左側恒流源工作,使總偏置電流變大,輸出緩沖級的驅動電流增大,比較電路速度加快;在V(GATE)為低時,左側的恒流源不工作,總偏置電流變小(此時LDMOS 不導通,過流比較器處于閑置狀態),為節能模式。

2.2 控制邏輯

控制邏輯模塊如圖4 所示,該模塊直接控制LDMOS 的開關。PULSE 信號的上升沿對應是CLOCK 時鐘的開始,PULSE 信號與時鐘CLOCK 的關系如圖9 所示。當發生過流時,OVERCURRENT信號為低,觸發器R 端為高,Q 為低,GateSwitch 信號為低,關斷LDMOS,從而實現過流保護功能。

圖4 控制邏輯電路圖

3 仿真結果

我們利用BCD 高壓工藝,在cadence 環境下進行電路仿真驗證。結果如下:

前沿消隱電路的仿真仿真條件:取電源電壓為5.8 V,2 pF 的電容在10μA 的放電電流情況下,延遲時間為Tdelay=C*0.

5VDD/I =2p*2.9/10μ= 0.58μs,仿真結果如圖5 所示。

圖5 前沿消隱電路仿真

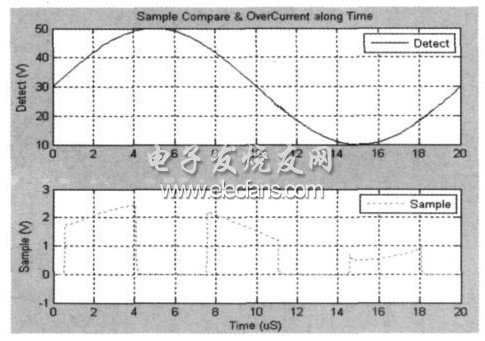

采樣電路的仿真

設檢測端電壓一般在10~50 V 之間變化,我們設置V(Detect)=SIN(30,20,50 k);周期為20μS;又設在采樣周期內,比較電壓為1 V;依據LDMOS管導通特性,設輸出漏電壓高于某值(本例為20伏)為過流,則分壓比設計為K = R4/ ( R3+R4)=5 k/(5 k+95 k)=1/20, 于是得到采樣電壓值為V(Sample)=V(Detect)*k =SIN(1.5,1,50 k),即最大值為2.5,最小值為0.5。同樣地,我們在采樣電路輸出端加上一個電容以消除電壓尖峰影響。該采樣電路仿真結果如圖6 所示。

圖6 采樣電路仿真

比較電壓產生器的仿真

在比較電壓產生器輸出端應加上電容Ccompare,以消除由于開關管導通的瞬間在Ccompare端產生的尖峰電壓,仿真結果如圖7 所示,其中虛/ 實線分別為有無電容存在時的仿真結果。顯然,電容Ccompare的存在極大地改善了輸出波形。電容Ccompare大小的選擇,應該權衡消峰效果、充電速度和芯片面積消耗間關系。

圖7 添加電容Ccompare 前后的比較

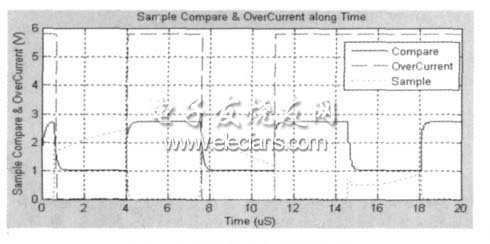

本例中,取Ccompare為4 pF。過流保護電路模塊的仿真

對圖3 進行電路仿真,電源電壓VCC 為5.8 V,LDMOS 漏端檢測電壓在10~50 V 之間,柵端電壓脈沖頻率為132 kHz,占空比為60%的方波,SPICE仿真條件設置為VCC=5.8 V,V (Detect)= SIN(30,20,50k),V (Gate)=PULSE(0,5.8,0.5u,0.5u,0.5u,3u,7u),仿真結果如圖8 所示。在1.26 uS~4.17 uS 和8.25 uS~11.2 uS 這兩個采樣區間內,采樣電壓V(Sample)較比較電壓V(Compare)大,輸出為低電平(過流保護,低電平有效);在15.2 uS~18.2 uS 采樣區間內,采樣電壓V (Sample) 較比較電壓V(Compare)小,輸出為高電平,對應不發生過流情況;其他時間段內柵電壓處于低電平,對應LDMOS處于關斷態,不可能發生過流,故過流輸出信號OverCurrent 為高電平。仿真結果表明,該電路確實能很好地實現過流保護的功能。

圖8 過流保護電路仿真結果

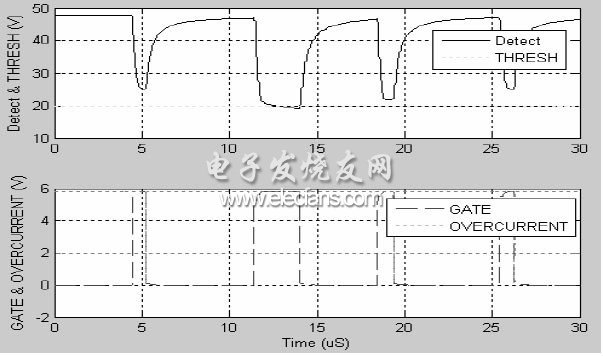

控制邏輯電路的仿真

在圖4 所示的控制邏輯中,設置時鐘CLOCK為PULSE (0,5.8,0,0,0,4u,7u), 過流信號OVERCURRENT 在15us 時從高電平跳變為低電平,進行仿真。PULSE 信號記錄了CLOCK 信號的開始, 并周期性檢測過流信號。當過流信號OVERCURRENT 低電平有效時,R 為高電平,將RS觸發器輸出Q 復位為低電平,此時FC 為高電平,柵控信號GateSwitch 輸出為低電平,關斷LDMOS。仿真結果如圖9(b)所示。

圖9 控制邏輯電路的仿真

閉環控制電路的整體仿真

如圖10 所示,圖3 電路和外接LDMOS 形成一個閉環控制系統。仿真結果如圖11 所示:在沒有發生過流時,柵極電壓的占空比最大;有過流發生時,過流信號OverCurrent 將柵極電壓強制設置為低電平,關斷LDMOS,從而達到了過流保護效果。

圖10 閉環總體仿真原理圖

圖11 閉環總體仿真波形

3 結論

本文闡述了幾種過流檢測方法,分析了每種方法的優缺點。設計了一款閉環控制型的過流保護電路,它采用直接檢測LDMOS 管漏端電壓的方法,可以克服采用電阻檢測時消耗能量,芯片容易發熱的缺點,同時提高了開關電源DC/DC 的能量轉換效率。另外,采取有比采樣電路設計,克服了工藝偏差的影響,提高了采樣精度。

基于3μm高壓BCD 工藝,我們在Cadence 設計環境中利用電路模擬器Spectre 對該控制電路進行了分模塊和整體模塊的仿真,結果表明該電路可以較好地實現實時過流保護功能。