摘要:提出一種基于FPGA" title="FPGA">FPGA的簡易數字示波器" title="數字示波器">數字示波器設計方法,硬件上采用以Altera公司的EP2C8Q208CN" title="EP2C8Q208CN">EP2C8Q208CN現場可編程門陣列芯片作為核心器件,同時結合FPGA和NIOS軟核的優勢,設計高效的片上可編程系統(SoPC)對高速A/D所采集的數據進行快速存儲和處理。整機測試表明,系統各功能正常,整個系統集成度高,體積小,可靠性高,易于程控,使用靈活。

關鍵詞:現場可編程邏輯門陣列;信號調整;高速A/D;片上可編程系統

高速數字化采樣技術和FPGA技術的發展對傳統測試儀器的體系結構,包括傳統測量方法、傳統儀器的定義和分類等都產生深刻的影響。伴隨數字技術的發展,數字示波器展現了其強大的功能:智能捕獲、參數分析、時頻等變換處理、超大規模數據波形存儲以及數據上網共享等。與傳統模擬示波器相比,數字示波器不僅具有可存儲波形,體積小,功耗低,使用方便等優點,而且還具有強大的信號實時處理分析功能。

1 系統組成

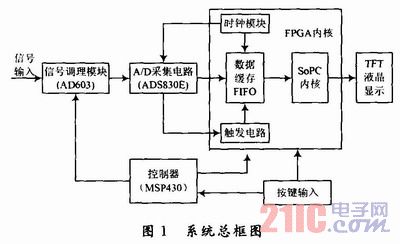

設計的數字示波器總體框圖如圖1所示。

系統主要包括信號調理模塊、A/D轉換模塊、控制器模塊、時鐘產生模塊、觸發電路、數據緩存模塊、數據快速處理模塊、輸入模塊及顯示模塊。控制器模塊由MSP430單片機組成,用來控制信號調理模塊和A/D轉換模塊以及按鍵輸入;時鐘產生模塊、數據緩存模塊,數據快速處理模塊這三個部分在FPGA內部完成;數據快速處理模塊是由基于FPGA的SoPC來完成的,同時SoPC還控制TFT液晶的顯示。

2 系統理論分析及硬件實現

2.1 信號調理模塊

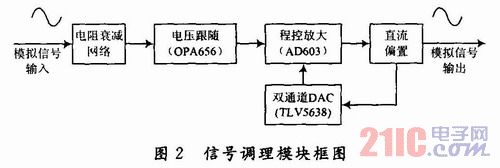

信號調理電路包括衰減網絡、電壓跟隨電路、程控放大電路和直流偏置電路等。信號調理電路框圖如圖2所示。

為了保證輸入信號在AD芯片的參考電壓范圍內,當大信號輸入時,必須通過衰減網絡對其進行衰減,以滿足A/D采集電路的電壓要求。通過電阻網絡分壓實現信號的衰減,衰減倍數有1/2和1/20兩種,通過單片機控制繼電器(TQ2-5),實現對兩種衰減倍數的切換;另外,電容網絡是進行相位補償,通過可調電容可以實現相位的補償。電壓跟隨電路作為隔離級,可減小后級電路對前級電路的影響。電壓跟隨電路由TI公司的OPA656構成,OPA656是寬帶單位增益穩定FET輸入運算放大器。

程控放大電路由程控增益芯片AD603和雙通道串口數/模轉換器TLV5638組成。單片機通過控制TLV5638的通道A產生高精度模擬電壓,用于調節AD603的放大倍數。直流偏置電路中,單片機控制TLV5638,使其OUTB引腳輸出一個直流電壓,該電壓經過NE5532組成的等比例反向器后接到OPA656的反向輸入端,可以通過這個電壓來確定OPA656的輸出,反映到屏幕上是波形的中線位置。如果液晶顯示的波形偏下或者偏上,可以調節TLV5638的B端輸出來調節。

2.2 采樣分析及A/D數據采集電路

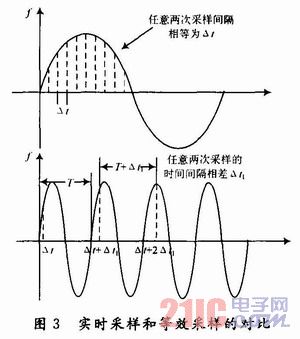

對于信號的采樣分為兩種方法,實時采樣和等效采樣。實時取樣對波形進行等時間間隔取樣,按照取樣先后的次序進行A/D轉換,并存入存儲器中。等效時間取樣方式是先采用“取樣技術”,將周期性的高頻信號變換成波形與其相似的周期性低頻信號,然后再做進一步的處理,因而可以比較容易地獲得很寬的頻帶寬度。但等效時間取樣僅限于處理重復性的周期信號。圖3是實時采樣和等效采樣的對比。

由于系統的最高時鐘為50MHz,綜合以上考慮和現實要求,該系統采用了等效采樣和實時采樣兩種采樣方式。當輸入信號頻率低于10M-Hz,選用實時采樣;反之,選用等效采樣。數據采集電路中AD芯片選用TI公司的ADS830E,它是一個單通道并行8位的模/數轉換器,采樣速率最高可達60 MHz。為了減少硬件電路的設計和消除其他信號的干擾,A/D數據采集中的采樣時鐘由FPGA提供。

2.3 單片機控制模塊設計

單片機控制模塊采用TI公司的MSP430F149單片機。MSP430F149控制信號調理模塊以及按鍵的輸入等。

2.4 系統中FPGA設計

2.4.1 時鐘分頻電路設計

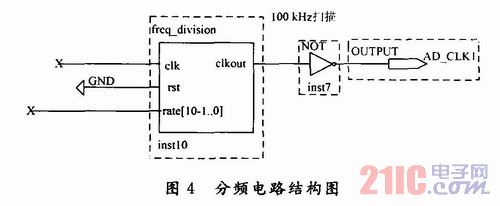

該數據采集系統具有比較寬的測量范圍,在FPGA內部設計了一個分頻電路,用來實現針對不同頻率的被測信號選擇不同的采樣頻率,確保采集數據更加精確。圖4是使用Verilog實現的分頻電路,該電路可以實現對50 MHz頻率的時鐘源進行分頻。分頻比可由程序控制,從而使時鐘滿足A/D采集的需求。

2.4.2 FIFO及觸發電路設計

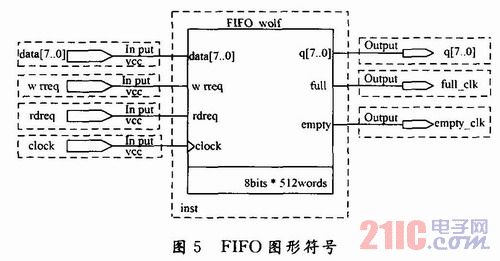

該系統利用FPGA設計大小為1 024 B的FIFO,實現對A/D采集數據的快速存儲。A/D采集電路開啟時,FIFO開始存儲數據。利用FPGA設計的FIFO如圖5所示。

當FIFO所存儲的數據在屏幕上還原出波形時,選取一個固定的起始點,使后面的波形能夠連續且沒有重疊的在屏幕上顯示。這個起始點反映到系統中就是觸發信號。該系統中采用內部軟件觸發方式,通過軟件設置觸發電平。所設置的施密特觸發器參數易于修改,從而抑制比較器產生的毛刺。當采樣值大于觸發電平,則產生一次觸發。該方式充分利用了FPGA的資源,減少外圍電路,消除硬件毛刺產生的干擾,易于調整觸發電壓。

2.4.3 SoPC系統設計

由于采集的數字信號需要進行高速處理,因此本設計利用了FPGA,高效的SoPC,對FIFO(數據緩存)中的數據進行處理,并控制TFT液晶顯示所采集信號的波形。

3 系統軟件設計

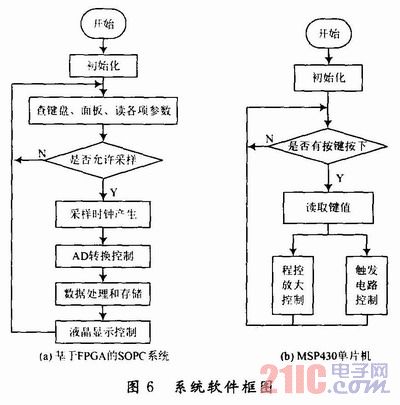

系統軟件設計實現了人機交互、信息提示、系統啟動與復位等功能。系統軟件設計如圖6所示,該系統包含采樣時鐘產生單元、顯存控制單元、TFT液晶顯示和可編程放大控制等模塊。Verilog可以形成原理圖,對其進行仿真實現,而且SoPC配置的軟核CPU允許掛接這些單元,很容易實現總體功能的合理規劃。

4 系統測試分析

(1)單次觸發掃描測試,觀察設計的示波器能否產生掃描電壓,并在信號上升沿開始顯示波形。觀察結果能夠產生掃描電壓,并顯示波形。

(2)經測量得到輸入短路時輸出噪聲的峰-峰值為1.72 mV。

(3)100 kHz方波校準信號的電壓幅值為0.308 V,誤差為0.69%。

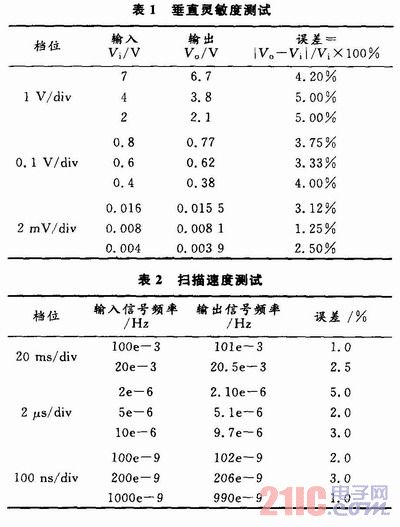

(4)垂直靈敏度測試。正弦信號頻率為10 kHz,記錄數據如表1所示。

由表2中數據可知,測量結果都在測量誤差允許范圍內,很好地完成了設計任務。

5 結語

該系統的突出特點采用FPGA作為核心控制器,同時結合NIOS軟核的優勢,實現了數字示波器的設計。結果表明,系統總體功能完善,集成度高,全數字化,體積小,重量輕,可靠性高,易于程控,使用靈活。